SCI论文(www.lunwensci.com)

摘要:为保证雷达射频信号数据采集及处理系统可靠性,提高数据传输速率,简化系统设计,设计了一款基于国产可编程逻辑门阵列(FPGA)和国产模数转换芯片(ADC)的射频数据采集及处理系统。系统核心器件为国产器件,能实现从雷达射频接收组件接收输入中频信号,在ADC中完成信号下变频、模数转换及数据采集功能;FPGA实现了ADC数据的接收、存储及上传功能。为解决LVDS协议传输数据较慢的问题,采用JESD204B串行传输协议,提高了数据传输速率。以N5166B信号发生器作为系统输入,对本系统进行验证和分析。结果表明:所开发的射频数据采集及处理系统可实现采样精度9位、采样频率400 Mbps/s、数据传输速率4 Gbit/s,提升了整体传输速率,满足功能和性能要求。

关键词:射频信号;数据采集;FPGA;国产化;电路设计

Design of RF Data Acquisition and Processing System Based on Domestic FPGA

Sun Yanping,Li Meng,Qu Wentao

(School of Mechanical Engineering,Xi'an Shiyou University,Xi'an 710065,China)

Abstract:In order to ensure the reliability of radar RF signal data acquisition and processing system,improve data transmission rate,and simplify system design,an RF data acquisition and processing system based on domestic programmable logic gate array(FPGA)and domestic analog-to-digital conversion chip(ADC)was designed.The core device of the system is a domestic device that can receive input IF signals from the radar RF receiver assembly,and perform signal down conversion,analog-to-digital conversion and data acquisition functions in ADC;through FPGA,the functions of receiving,storing,and uploading ADC data were realized.In order to solve the problem of slow data transmission in LVDS protocol,JESD204B serial transmission protocol was adopted to improve the data transmission rate.The N5166B signal generator was used as the system input,the verification and analysis of this system were carried out.The results show that the developed RF data acquisition and processing system can realize a sampling accuracy of 9 bits,a sampling frequency of 400 Mbps/s,and a data transmission rate of 4 Gbit/s,by which the overall transmission rate can be improved,and it meets functional and performance requirements.

Key words:RF signal;data acquisition;FPGA;localization;circuit design

0引言

高速射频数据采集设备主要应用于雷达、通信、测量等领域[1]。目前国内外射频采集及处理器件选型方面仍以进口芯片为主,其中射频接收ADC芯片主要的供应商为美国AD、TI、亚德诺等公司,大规模FPGA芯片大都选用美国Xilinx、Altera等公司产品。近年来,随着计算机、微电子等相关科学技术逐步逼近美国高端产业,以美国为首的西方联盟国家,对中国关键领域的大规模集成电路限制供应,因此发展自主可控的计算机软硬件平台[2],开展国产化替代设计,提高安全自主能力尤为迫切[3-4]。

文献[5]基于AD9154和Xilinx的ZC706搭载的ZYNQ7000 FPGA主控芯片实现高速复杂雷达波形设计,使用JESD204B接口传输数据,但器件都来自国外厂家。文献[6]设计了基于苏州云芯微电子ADYA16D125和复旦微电子JFM7K325T-N FPGA芯片的全国产器件的短波接收机,使用PCIE接口,数据传输速率相对较慢。文献[7]设计了基于JESD204B的1.0 Gsample/s高速数据采集系统,该系统使用了本振芯片ADF4351、正交解调芯片ADL5380、可变增益放大器AD8366、模数转换芯片ADS5J60和Xilinx Virtex-7系列FPGA芯片,芯片数量较多,电路设计较为复杂。

为进一步提高数据传输速率,增强系统可靠性,简化设计,本文通过对国产高速数据采集及处理系统芯片进行应用研究,设计整体系统功能替代方案,开发一款基于国产可编程逻辑门阵列(FPGA)和国产模数转换芯片(ADC)的射频数据采集及处理系统。并完成方案验证,为有效降低数据采集及处理系统芯片依赖进口的问题提供了一种可行方案。

1系统总体设计方案

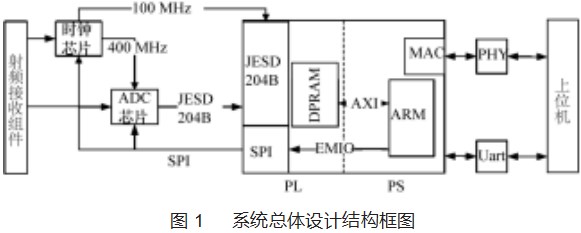

系统的总体设计核心主要包括射频接收ADC模块和FPGA主控模块两部分。总体设计结构框图如图1所示。其中,ADC模块包括ADC下变频、模数转换和ADC时钟设计;FPGA主控模块包括PL侧JESD204B接口、SPI接口、DPRAM设计和PS侧网络、串口收发控制器设计。

如图1所示,射频接收组件完成雷达信号的调制,给系统提供400 MHz时钟信号和ADC芯片500 MHz射频信号输入。时钟芯片收到400 MHz时钟信号后进行分频处理,将同步的400 MHz时钟信号和100 MHz差分时钟信号分别送给ADC芯片GM4680和FPGA芯片FMQL45T9 00内的JESD204B总线,以满足射频经过模数转换后数据的同步接收。ADC芯片接收到500 MHz射频信号后,首先对接收的信号进行数字下变频处理,实现零中频解调,然后再将模拟信号转换为数字信号,通过JESD204B串行传输总线将数据传输到FPGA中PL端,完成数据的接收。

在FPGA主控模块中设计了JESD204B总线接收端逻辑,以完成与ADC之间以4 Gbit/s速率对数字信号的接收与处理。然后,将采样数据存储到PL侧的DPRAM中,DPRAM与PS侧则通过AXI总线实现数据交互。SPI接口由PS侧扩展复用的输入/输出(EMIO)到PL侧,完成时钟芯片和ADC功能寄存器的配置。PS侧通过AXI总线将DPRAM中数据读出,将数据打包成报文用网络传输方式发送至上位机,上位机与FPGA之间通过422串行收发控制器(UART)下发指令,控制数据上传。

2 ADC模块设计

2.1国产ADC芯片选型

综合国产ADC芯片的比测以及对芯片功能的需求情况,选用国内成都振芯科技的GM4680 ADC芯片。GM4680内部集成数字下变频(DDC)、频率搬移、低通半带滤波器和模数转换功能,以往设计中下变频、频率搬移和低通半带滤波器功能需在电路和FPGA芯片中完成,而集成到ADC芯片中,可减少对FPGA资源的需求,降低电路板层数和电路设计复杂度。GM4680是一款低功耗、高带宽14位、采样速率高达1 GSPS的双通道ADC,采用JESD204B高速串口简化系统布线连接,满足各类高性能模拟基带信号的数据采集要求,每个ADC支持1 lane、2 lane或4 lane数据通道,数据传输速率范围支持1.25~10 Gbit/s宽范围工作。

2.2数字下变频

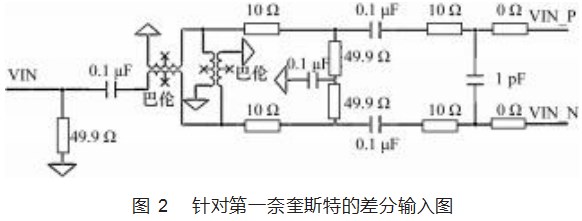

射频接收组件传输500 MHz射频信号,首先经过针对第一奈奎斯特频率差分输入的双巴伦设计,完成单端转差分和阻抗匹配,如图2所示。

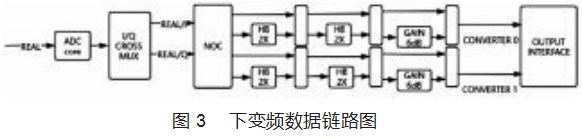

其次,GM4680收到转换的差分信号,在内部将500 MHz频率搬移到100 MHz,对其进行半带抽取滤波器和增益控制器设计,下变频主要用于降低数据速率和滤波,设计数据链路如图3所示。

其中,GM4680支持两路ADC通道和DDC通道。射频接收组件输入的500 MHz射频信号为实数信号,从一路ADC通道进入,经过DDC通道进行实数到复数变换,输出相位相差90°的I、Q两路信号,I、Q两路信号叠加载波发生器(NCO)产生的本振信号,将信号搬移到零中频信号进行输出。

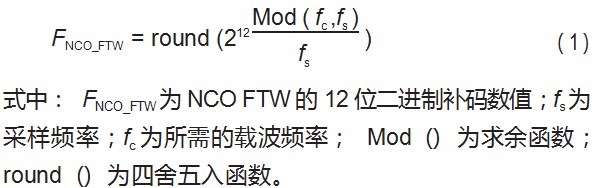

GM4680的频率搬移模块支持4种不同的中频模式,设计中采用NCO可调节的可变中频模式,计算NCO频率协调字(FTW)频率搬移数值。其频率协调字控制位宽为32位,相位偏移字(POW)位宽为16位,NCO频率值由输入NCO_FTW的12位二进制补码数决定,POW用来建立GM4680内部各DDC之间的相位关系,FTW可通过式(1)计算:

叠加信号频率搬移到零中频后,经过两级半带滤波器,将输出的I/Q正交信号进行4倍抽取,降低采样速率,提供充分的混叠抑制,同时防止目标带宽周围的无用邻近载波影响信号。将实数输入信号下混频至基带时,由于对负镜像的滤波,信号存在6 dB的损失。因此,为将信号的动态范围中心重新定位在输出位的满量程中,滤波后附加DDC增益级中的6 dB增益补偿损失。

2.3模数转换

GM4680内核采用多级、流水线架构,模拟输入为一个差分的输入缓冲器,输入缓冲器为模拟输入信号提供400Ω终端电阻,每一级流水线的量化输出被合成为14位数字逻辑,具有DNL<±0.4LSB,INL<±3LSB的高线性度。

2.4时钟管理

JESD204B传输链路稳定的关键是高质量的时钟,传输协议要求发送接收端器件的时钟必须是同源时钟[8],时钟不同源时,JESD204B中sync同步信号会频繁短暂链接失败,时钟采样信号时会出现滞后现象,导致数据采集不准确。射频接收组件发出400 MHz时钟信号,经过巴伦后进入时钟管理模块,时钟管理模块主要为GM4680和FPGA提供JESD204B同步时钟。

时钟芯片用的是国产GM4526C芯片,是一款提供亚皮秒级抖动性能的时钟分配器,片上集成电压控制振荡器(VCO)和锁相环,可以提供GM4680采样时钟和确定性延迟SYSREF时钟,满足设计中JESD204B时钟需求。设计中通过SPI协议先完成GM4526C的时钟分频与输出配置,再配置GM4680的下变频功能。

FPGA的高速串行收发器GTX接收通道数据宽度为32位,而GM4680单通道输出数据为8位,所以GM4526C提供与采样率相对应的400 MHz的器件时钟给GM4680,为FPGA提供100 MHz的时钟。FPGA接收数据时钟为GM4680采样时钟频率的1/4,是为了匹配JESD204B协议传输中发送端和接收端之间的数据速率。

3 FPGA主控模块设计

3.1国产FPGA芯片选型

FPGA主控模块设计将DSP+FPGA功能集成在国产ZYNQ系列芯片中,选用了国产复旦微电子的FMQL45T900芯片,FMQL45T900芯片集成了四核ARM处理器处理系统(PS)和可编程逻辑(PL),配合相应的开发软件,实现一体化软硬件平台,支持QSP接口、USB总线接口、DMA控制器、千兆以太网等多种通信接口[9]。片内集成AXI总线完成PL端和PS端的通信,集成GTX串行高速收发器IP核,支持最高12.5 Gbit/s的线速率,满足JESD204B接口速率要求。

3.2 JESD204B接口

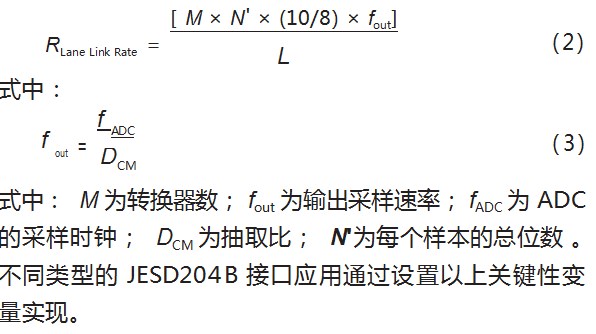

JESD204B接口主要用于模数/数模转换器和逻辑器件之间的高速数据传输,包括3个子类:子类1、子类2和子类3[10-12],3个子类的区别在于同步方式不相同。系统采用子类1的同步方式,在FPGA中设计了JESD204B接收端逻辑。JESD204B接口建立链接过程分为3个阶段:(1)FPGA用时钟管理模块发送的100 MHz时钟,内部生成SYSREF信号发送出去,GM4680和FPGA的JESD204B接收端收到SYSREF信号后,内部器件时钟(Device Clock,DCLK)、帧时钟(Frame Clock,FC)和本地多帧时钟(Local Multi-Frame Clock,LMFC)等时钟进行相位同步;同时FPGA将sync信号拉低,GM4680检测到sync拉低后,在下一个LMFC上升沿开始代码组同步(Code Group Sync,CGS)过程,持续1个LMFC周期;(2)CGS过程完成后,在下一个LMFC周期开始初始化通道同步(Initial Lane Alignment,ILA)过程,调和不同长度的走线以及接收器导致的字符偏斜,ILA过程持续4个LMFC周期;(3)最后开始数据传输过程(Da‐ta Transmission),GM4680开始持续在链路上发送有效数据。

数据输出采用8B/10B编码[13],其通道线路速率与JESD204B参数满足以下关系:

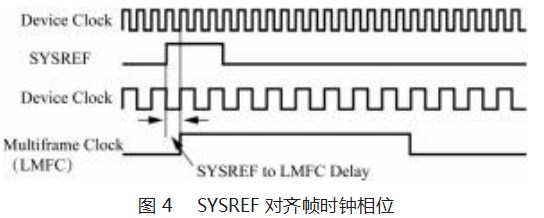

3.3 SYSREF确定性延时信号

SYSREF对齐JESD204B链路上的时钟初始相位,如图4所示。

主要有3种工作模式:脉冲模式、周期模式和间歇周期模式,周期必须为LMFC的整数倍,设计中采用脉冲模式。FPGA器件时钟和SYSREF使用同一时钟基准,最小化两者间的时钟偏斜[14],时钟芯片传输到FPGA的100 M差分时钟,在PL侧使用IBUFDS_GTE2原语和BUFG全局时钟缓冲器,将差分时钟转为单端时钟信号,以转换的单端时钟信号为基准,在FPGA PL侧产生SYS‐REF确定性延时信号,再经OBUFDS原语将SYSREF信号转换为ADC可以接收的差分信号输出,其中,SYS‐REF差分信号输出需要加100Ω的匹配电阻[15]。

3.4 DPRAM

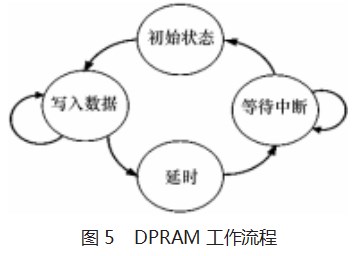

在Vivado软件的Vivado Block Design中搭建双口RAM,FPGA PL侧接收到JESD204B传输的有效数据后,将数据按需求存储到DPRAM中,PS侧通过AXI总线协议读取DPRAM数据。

DPRAM工作流程如图5所示,在初始状态收到FP‐GA有效信号后开始以100 M速率向DPRAM写入,传输数据为流式数据;一波数据写完进入延时等待状态,由于PS侧读取数据后需要进行数据打包、上传至上位机,速率较慢,PL侧增加延时等待机制,延时结束后PL发送中断信号给PS,进入中断等待状态;PS中断进程响应后开始处理数据,处理完成后通过AXI_GPIO回传信号,表示数据已经接收,PL检测到AXI_GPIO信号,重新进入初始状态。

3.5网络接口

FPGA与上位机之间使用1 000 M/100 M自适应以太网进行数据传输,FPGA PS侧集成2个以太网控制器(GMAC),支持全双工模式,由于管脚资源限制,MIO只支持RGMII方式,GMII需要EMIO到PL侧实现。采用国产厂家裕泰车通的PHY芯片,与FPGA之间采样RGMII接口进行连接,通过MDIO接口配置管理PHY芯片,采用小端字节顺序发送网络传输数据。

3.6串行收发控制器

FPGA PS端MIO一路异步串行收发控制器(UART)接口,控制器外接422串口芯片,通过串口接收上位机发送指令,控制GM4680数据采集的开始和停止。

4测试结果

测试中使用2台是德科技公司N5166B型号信号发生器作为系统输入,对本系统采集射频信号数据和下变频频谱的测试结果进行验证和分析。N5166B输出频率范围为9 kHz~6 GHz,标配输出功率最大+18 dBm,满足射频信号频率及功率模拟要求。

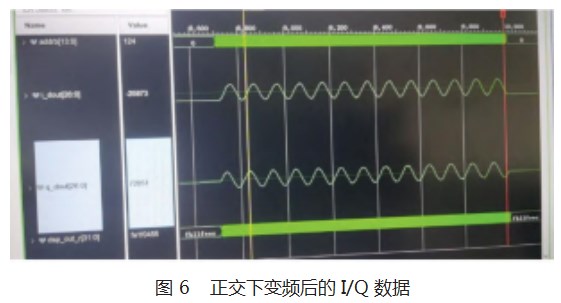

一台设备模拟输入的400 MHz时钟信号,另一台设备模拟射频信号源,设置信号源对系统输入520 MHz的模拟正弦波信号,观察FPGA接收到设备的采样数据,通过Vivado软件的调试核心逻辑分析仪ILA抓取缓存到FPGA内部的数据,如图6所示。

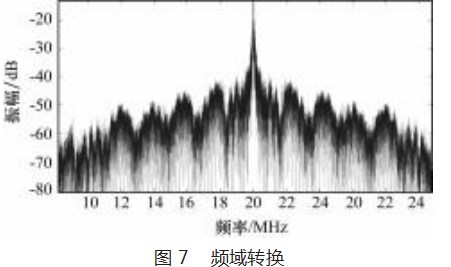

信号发生器发出一波数据,在GM4680中经过实复信号变换。由图6可见,FPGA采集到i_dout和q_dout数据输出信号,两路数据信号为整体相位相差90°的I、Q信号,且接收基带信号数据良好。将数据保存为csv文件后,对保存数据进行FFT分析。由图7可以看出,数据转为频域信号后,系统将信号发生器输入的520 MHz模拟信号在GM4680中进行下变频后,采集到的零中频整波数据频率为20 MHz,符合设计预期结果。

5结束语

本文针对雷达射频数据采集系统工程需要,设计出基于国产器件的高速数据采集系统。该方案设备组成简单、系统稳定且核心器件自主可控,满足射频信号的数据采集需求,为国产高速数据采集传输系统提供了一种可行性方案,且本系统在国产化设备需求迫切的当下具有一定的应用价值。但是,国产器件之间的兼容性具有不确定性,未能进一步做提升系统数据采集速率的实验,后续还需要在提升数据采集传输速率以及采样精度两方面做针对性的研究。

参考文献:

[1]WU Z,ZHANG C,LI F,et al.High speed serial interface trans‐ceiver controller based on JESD204B[C]//2016 14th IEEE Inter‐national New Circuits and Systems Conference(NEWCAS).IEEE,2016:1-4.

[2]胡钢.基于龙芯3A2000处理器的网络安全平台设计与应用[J].机电工程技术,2020,49(2):120-122.

[3]李溪野.基于国产器件的MIMO-SCFDE系统硬件平台的设计与实现[D].北京:北京邮电大学,2017.

[4]王育才,包晓军,刘远曦,等.一种基于国产ADC的高速信号采集系统[J].电子世界,2020(13):19-20.

[5]黄云青,张佳琦,白森.基于AD9154和FPGA的高速复杂雷达信号波形的设计[J].航空兵器,2020,27(1):76-80.

[6]赵一超.一种基于全国产器件的PCI-e短波接收机的设计方法[J].电脑知识与技术,2021,17(20):165-167.

[7]和爽,王红亮.基于JESD204B的射频信号高速采集系统设计[J].电子器件,2020,43(1):124-127.

[8]宛强,郭金翠,王巍,等.JESD204B接收系统同步技术研究与实现[J].电子器件,2018,41(6):1566-1571.

[9]宋凯.基于ZYNQ的多丝探测器数据采集系统的研制[D].兰州:中国科学院大学(中国科学院近代物理研究所),2020.

[10]林云,张祥,黄跃,等.基于Zynq-7000的毫米波雷达数据采集系统设计[J].电子测量技术,2021,44(19):134-138.

[11]LI X,LIU Y.Efficient implementation of the data link layer at the receiver of JESD204B[C]//2019 International Conference on Intelligent Computing,Automation and Systems(ICICAS).IEEE,2019:918-922.

[12]金东强.JESD204B协议关键技术研究[D].无锡:江南大学,2019.

[13]陈婷婷,陆锋,万书芹,等.符合JESD204B协议的传输层电路设计[J].光通信技术,2022,46(1):86-90.

[14]刘仁华.多路射频同步采集系统设计与实现[D].武汉:武汉大学,2019.

[15]刘宁宁,王传根,王乐,等.基于JESD204B协议的多通道高速采集系统设计[J].电子信息对抗技术,2021,36(2):83-87.

关注SCI论文创作发表,寻求SCI论文修改润色、SCI论文代发表等服务支撑,请锁定SCI论文网! 文章出自SCI论文网转载请注明出处:https://www.lunwensci.com/ligonglunwen/61509.html