SCI论文(www.lunwensci.com)

摘要:针对角位置测量电路存在的计数脉冲信号处理频率较低和抗干扰性差的缺点,设计了一种以C8051F020 单片机、MAX 7000AE 系列现场可编程门阵列(Field-Programmable Gate Array,CPLD) 和MC3486 差分脉冲信号处理芯片为核心元件的多通道光 电编码器脉冲信号测量电路;分别设计了CPLD 的四倍频、脉冲计数及判向逻辑电路和VHDL 程序;通过使用高精度光电编码器, 满足了在高转速条件下,大幅提升角位置测量精度,并可方便地进行多测量通道扩展的要求。对影响高频脉冲计数电路正常工作的 各类外部干扰因素进行分析,使用高频脉冲进行采样比较的方法,设计了一种由检测脉冲沿得到的DIR 判向信号作为D 触发器的 选通信号的方法,以滤除计数脉冲上的毛刺干扰信号,从而保证了单方向计数,降低了发生误计数的可能性;并通过Quartus II 软 件对所设计方法输出信号的时序功能进行了仿真,并验证了该电路设计方案的正确性。

关键词:角位置测量,光电编码器,CPLD,VHDL

Design and Implementation of a Multi-channel Angular Position

Measurement Circuit for Servo System

Yang Rui,Xia Tao,Huang Ying

( School of Electric Power Engineering,Nanjing Institute of Technology,Nanjing 211167.China )

Abstract:For the shortcomings such as receiving low frequency pulse signal and poor immunity in the angular position measuring circuit,a multi-channels photoelectric encoder signal measurement circuit which is based on C8051F020 MCU,MAX 7000AE series CPLD and MC3486 differential pulse signal processing chip is designed.The VHDL procedures and CPLD internal logic circuits for the fourfold frequency direction judgment circuit and pulse counting circuit are designed.With a high-precision photoelectric encoder,it meets the requirements of greatly improving the angular position measurement accuracy under high-speed conditions,and can easily expand multiple measurement channels. Analyze various external interference factors that affect the normal operation of the high-frequency pulse counting circuit,use high-frequency pulses for sampling and comparison,and design a DIR direction judgment signal obtained by detecting the pulse edge as the gate signal of the D flip-flop The method to filter out the burr interference signal on the counting pulse,thus ensuring one-way counting and reducing the possibility of miscounting;And by Quartus II software,the timing sequence function of the output signal of the designed method is simulated,and the correctness of the circuit design scheme is verified.

Key words:angular position measurement;photoelectric encoder;CPLD;VHDL

引言

高精度的角位置测量电路作为角位置伺服控制系统中位置跟踪回路闭环控制的重要反馈,完成了角位置反馈信号的产生、调理和传输的任务,直接决定了伺服控制系统角位置的控制精度[1]。角位置测量电路系统中的传感器,一般多采用基于霍尔原理的高精度光电编码器,由其产生包含角位置信息的差分脉冲信号。文献[2 ] 介绍了一种采用圆光栅和水平电容传感器作为测角元件的测量方案。角位置处理电路模块,一般多由各种高性能嵌入式系统和与之配合的外围逻辑电路构成,完成较 为复杂的逻辑运算和信号调理功能。文献[3 ] 介绍了一种基于RTlinux 嵌入式处理系统配合AD2S80A 轴角变换器角位置信号调理电路。经过以上过程处理最终将得到最终的角位移数值作为反馈信号,送至伺服控制计算机构成位置闭环。文献[4 ] 介绍了一种基于FPGA 控制芯片和LMD18 200 驱动芯片,采用RS422 通信串口完成 步进电机角位置信号闭环的伺服系统,具有控制灵活、操作简单、控制精度高和扩展性极强的特点。传统的基 于分立元件式的角位置测量电路系统,由于模块内部集成度较低,存在抗电磁干扰能力差,易产生误计数脉冲信号,并且高频率计数工作不稳定等问题,降低角位置测量的精度。因此,设计一种精度高,抗干扰信号能力 强的角位置测量电路对提高位置伺服控制系统的快速跟踪性能起着至关重要的影响[5-7] 。本文采用光电编码器作为测角元件、可编程逻辑器件CPLD 为核心设计了测量信号电路,相较于传统的测角测量电路系统,能大幅度提高测角系统的性能。

1 角位置测量电路的主要功能

1.1 总体结构设计

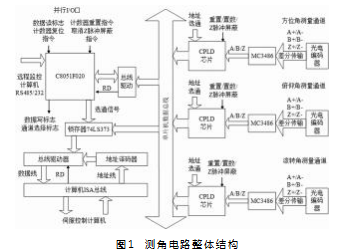

在三轴系得稳定平台伺服控制系统中,存在方位角、 俯仰角和滚转角3个旋转轴系的实时角位置测量反馈[8]。 因此,设计了3条测角通道,每条通道均包含1个光电 编码器,差分处理电路和现场可编程门阵列( Field- Programmable Gate Array,CPLD),由1根8位数据总线, 经过总线驱动控制的分时控制,送入单片机中处理; 通过高速单片机的外部接口,与伺服控制计算机实时 交换3条通道的角位置测量数据,以供稳定控制算法进行复杂的坐标系解算操作。测角电路整体结构如图1 所示。

在各级芯片选型方面,单片机模块采用Cygnal 公司 生产的SOC 型8位高速单片机C8051F020.最大处理能力 可达25 MI/s (million instructions per second );CPLD 模块 采用Altera 公司的MAX7000AE 系列的EPM7256AETC100.集成度规模为5000 可用门、256 个宏单元和16 个逻辑阵列块,工作频率为172.4 MHz;差分脉冲信号处理模 块采用Motorola 公司的MC3486 芯片,最大接收脉冲频率 约为28 MHz。由于采用了高速型单片机,可以在0.5 ms内对各通道计数值实时采集和处理并输出到伺服控制计算机接口。

1.2 工作原理分析

以图1中的方位角测量通道为例,在测量电路的输 入端,MC3486 芯片分别接收光电编码器输出的3组差分 脉冲信号A +和A-、B +和B-、Z +和Z-,将其分别转换成单端脉冲信号A、B 和Z。单端脉冲信号A、B 经过CPLD 芯片内的逻辑电路处理后,最后可以得到24 位二进制编码形式输出的角位置计数值。三条测角通道的CPLD 之间均通过8位数据总线和总线驱动控制器与高速单片机C8051F020 相连,根据单片机的4位地址总线分 别选通,采用分时的方法去依次读入三条测角通道的24 位角位置计数值。单片机通过发送选通信号,将计数值输出到锁存器74LS373 进行锁存。伺服控制计算机以总 线驱动器74LS245 作为缓冲器通过16 位ISA 总线读取数据作为位置反馈量形成闭环控制。ISA 总线的地址信号经过译码后作为选通信号,附加读写控制信号,可以实现单片机和伺服控制计算机之间传输多个测角通道的数据。

1.3 CPLD 内部功能设计

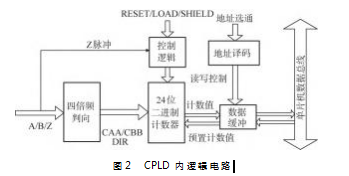

根据角位置测量电路的功能要求,将CPLD 内部逻 辑划分为:四倍频判向、计数器、数据接口、地址译码 和复位逻辑等主要模块[9]。逻辑电路的原理结构如图2所示。

经MC3486 处理后的角位置单端信号A、B 和Z由引脚引入CPLD 片内,经过倍频判向模块后得到4倍频的计数脉冲CAA 和CBB 以及判向信号DIR;计数脉冲送入24 位计数器模块处理,并根据判向信号DIR 电平的高 低,确定正、反转计数值的增加;数据缓冲模块采用带 选通功能的24 个D 触发器组成,24 位二进制数据缓冲锁存与单片机的8位数据总线接口进行通信;单片机的4 位地址总线与CPLD 的地址译码模块相连,实现对3条计数通道CPLD 的选通控制;控制逻辑模块接收单片机发送的RESET、LOAD 和SHIELD 信号以实现对计数器值的复位, 置位和取消对ZERO 脉冲的屏蔽功能。同时,当角位置转到ZERO 脉冲信号产生的位置,ZERO 脉冲通过控制逻辑模块对计数器清零,并实现对角位置的寻零过程[10] 。测量电路的实物如图3所示。

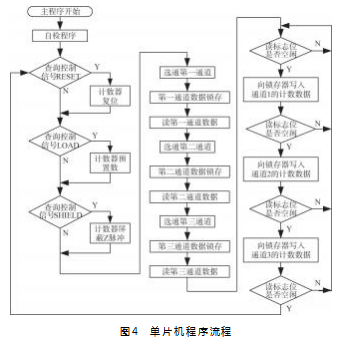

1.4 单片机程序设计

测量电路的单片机程序主要完成以下功能。测量电路和单片机上电后,首先查询并行数字I/O 口的3个标 志位,以判断当前是否需要对计数器复位,重置或取消ZERO 脉冲屏蔽,并进行相应的处理;随后依次选通3 条CPLD 通道,对计数器进行锁存,利用8位数据总线 按照高、中和低3个字节依次传送24 位角位置计数值,并存入单片机缓存中;接下来查询伺服控制计算机的读标志位是否空闲,如果空闲,则置位数据写标志位和通 道选择标志位,向74LS373 锁存器写入相应通道的计数 数据,写完后清除数据写标志,若控制计算机正在进行 读操作,则等待至读标志位清除。依次向控制计算机传 送3条通道的角位置计数值,最后程序循环操作,重新开始查询I/O 口标志位。程序流程如图4所示。

2 CPLD 主要逻辑功能实现

2.1 四倍频逻辑电路设计

四倍频逻辑电路的主要功能是对经过MC3486 芯片转换后的输入单端脉冲信号进行重新调理,并对信号的 频率进行四倍处理,从而提升伺服系统的控制精度,具体逻辑功能设计如下。

使用VHDL 语言定义信号AA 和BB,表示光电编码器的输出信号经过MC3486 处理后的单端脉冲信号A 和B;定义信号CLK0.表示系统时钟信号。使用D 触发 器,把两个单端脉冲分别延时一个系统时钟周期,得到 AA1 (0 ) 和AA1 ( 1 ) 两个辅助信号;将这两路脉冲信 号分别通过D 触发器再延时一个系统时钟周期后,得到 BB1 (0 ) 和BB1 ( 1 ) 两个辅助信号。将产生的四组辅助信号经过组合逻辑运算后得到CAA 和CBB 两路脉冲信号输出,实现对AA 和BB 的四倍频,具体程序设计如下。

FOURFOLD:PROCESS(AA,BB,CLK0)

BEGIN

IF rising_edge ( CLK0 ) THEN

AA1 (0 ) <=AA;

AA1 ( 1 ) <=BB;

BB1 (0 ) <=AA1 (0 );

BB1 ( 1 ) <=AA1 ( 1 );

END IF;

CAA<= ((( NOT AA1 (0 ))AND BB1 ( 1 )AND ( NOT AA1 ( 1 ))) OR((( NOT AA1 ( 1 )) AND AA1 ( 0 ) AND ( NOT BB1 ( 0 ))) OR ((( NOT AA1 (0 ))AND BB1 (0 ) AND AA1 ( 1 ))) OR ( AA1 (0 ) AND AA1 ( 1 )AND ( NOT BB1 ( 1 )));

CBB <= (( NOT AA1 (0 )) AND BB1 (0 ) AND ( NOT AA1 ( 1 ))) OR(AA1 (0 ) AND AA1 ( 1 ) AND ( NOT BB1 ( 1 ))) OR ( AA1 (0 ) AND BB1 ( 1 ) AND ( NOT AA1 ( 1 ))) OR (( NOT BB1 ( 0 )) AND AA1 ( 0 ) AND ( NOT AA1 ( 1 )));

END PROCESS;

当电机正转时,CAA 有脉冲输出,CBB 输出为低电 平;反转时,CBB 有脉冲输出,CAA 输出为低电平,其对应内部逻辑电路如图5所示。

2.2 判向逻辑电路设计

光电编码器的输出信号有如下特点,如果A 码道脉 冲超前B 码道脉冲90°,则判定光电编码器正转;反之 如果B码道脉冲超前A 码道脉冲90°,则判定光电编码 器反转。根据这一特点,采用检测脉冲沿的方法实现判 向信号DIR 输出。当脉冲AA 在上升沿时,判断BB 脉冲 电平值,如果BB 为高电平,表示电机反转,将判向信 号DIR 置为0;反之,则为电机正转,将判向信号DIR 置为1.程序设计如下。

DIRECTION:PROCESS( AA,AB )

BEGIN

IF rising_edge ( AA) THEN

IF( BB =‘1’)THEN

DIR <= ‘0’;

ELSE

DIR <= ‘1 ’;

END IF;

END IF;

END PROCESS;

2.3 脉冲计数电路设计

脉冲计数器逻辑电路采用两组独立的计数器,分别对四倍频判向电路模块输出的CAA 和CBB 脉冲信号进行计数,输出COUNTER1 为正转计数信号,COUNTER2为反转计数信号。

正转计数器COUNTER1 的VHDL 程序如下。

COUNT1:PROCESS( CAAOUT,ZERO,CLOAD)

BEGIN

IF( ZERO= ′1′)THEN

COUNTER1 < ="000000000000000000000000"; ELSIF CLOAD= ′1′THEN

COUNTER1 <=PRELOAD;

ELSIF rising_edge ( CAA)THEN

COUNTER1 <=COUNTER1 + ′1′;

END IF;

END PROCESS;

反转计数器COUNTER2 的VHDL 程序如下:

COUNT2:PROCESS( CBBOUT,ZERO,CLOAD)

BEGIN

IF((ZERO = ′1′) OR ( CLOAD = ′1′))THEN

COUNTER2 < ="000000000000000000000000";

ELSIF rising_edge ( CBB )THEN

COUNTER2 <=COUNTER2 + ′1′;

END IF;

END PROCESS;

正、反转计数器COUNTER1 和COUNTER2 分别在CAA 和CBB 脉冲的上升沿触发计数,保证计数值的准确 性。最终,根据正、反转的计数器的数值再进行运算后,得到实际的角位置计数值。

VHDL 程序设计如下:

COUNT:PROCESS ( COUNTER1.COUNTER2)

BEGIN

IF rising_edge ( CLK0 ) THEN

COUNTER < =COUNTER1-COUNTER2;

END IF;

END PROCESS;

在程序中,由于CPLD 内部电路的工作频率较高,在传输24 位数据时会由于传输延时的差异导致某一位赋值错误,因此设计了采用等待系统时钟CLK0 的上升沿,再进行C OUNTER1 - COUNTER2 的运算后,值赋给COUNTER 操作,使得计数器的可靠性明显得到提高。 此外,当计数器接收到单片机发来的清零信号ZERO 为1时,对正、反转计数器同时清零;当接收到 预置角位置计数值信号CLOAD 为1时,因为默认均为预 置正向角位置值,所以对正转计数器COUNTER1 预置值 PRELOAD,而对反转计数器COUNTER2 清零。

2.4 计数脉冲防干扰设计

由于光电编码器的抖动以及角位置测量信号传输中受到的各类干扰等会使光电编码器输出脉冲上混有毛刺信号,这些毛刺信号会引起误计数,高频率计数工作不稳定等问题,降低角位置测量的精度[11-12] 。因此,需对图5所示四倍频判向逻辑电路输出的CAA 和CBB 信号重新进行处理,以避免误计数脉冲(毛刺信号) 对实际脉冲信号的计数影响。具体逻辑电路设计原理如图6所示。

根据逻辑电路原理图,将CAA 和CBB 分别接在D 触发器D1 、D2 的D输入端,以系统时钟信号CLK0 作为 这两个D触发器的时钟,当CLK0 信号的上升沿,CAA 和CBB 才会被输入D 触发器,这样两个信号由于竞争冒 险产生的干扰毛刺信号将会很窄,大部分的高频干扰信 号将被滤除。同时,将检测脉冲沿方式得到的DIR 判向 信号作为D 触发器的选通信号ENA,当DIR 为1时,选 通触发器D1 使能端,在CLK0 时钟上升沿,CAAOUT 输 出信号,而触发器D2 未选通使能端,CBBOUT 保持不 变,反之则CBBOUT 输出,CAAOUT 保持。这样既滤除 了计数脉冲CAA 和CBB 上的干扰信号,又保证了单方 向计数,进一步降低了误计数的可能性,提高了系统的可靠性。

VHDL 程序设计如下。

FILTER:PROCESS( CAA,CBB,CLK0.DIR)

BEGIN

IF rising_edge ( CLK0 ) THEN

IF( DIR=‘1’)THEN

CAAOUT <=CAA;

ELSE

CBBOUT <=CBB;

END IF;

END IF;

END PROCESS;

3 仿真结果验证

3.1 仿真环境分析与设计

伺服控制系统中采用的是长春禹衡光学有限公司生产的LFA-500 A-18000 型高精度增量式光电编码器,其 编码盘每圈有18 000 个透光窗,每旋转1圈,可以差分 信号方式输出18 000 个A 脉冲(正转)和B 脉冲(反 转)[13 ] 。因此,光电编码器的测量分辨率为:λ =360°/ 18 000 =0.02°;而伺服控制系统对角位置测量的精度要 求为λ′=0.005°,来自于光电编码器的计数脉冲经过四 倍频判向逻辑电路处理后,可使得控制精度达到要求, 即测角精度达到λ=λ′=360°/( 18 000 × 4 ) =0.005°;伺 服平台各轴系在额定负载条件下的最大角速率为:ω max =25 ( ° )/s,即光电编码器所输出的计数脉冲的最高频率 可达fmax =ωmax/λ′=5 kHz,由于计数脉冲的占空比为1∶ 1. 则普通计数脉冲的宽度为pwidth = Tmax/2 = 1/(5 kHz × 2 )=100 μs。

接下来,利用Quartus II 软件,对CPLD 芯片的各引 脚进行详细定义,选择合适的各元件布线方式,用硬件 描述语言VHDL 建立各模块的功能模型,编译后在Quartus II 软件中通过时序功能仿真以验证逻辑电路工作 的正确性。[14 ]

3.2 四倍频判向电路仿真结果验证

根据以上分析和计算,对四倍频判向逻辑电路进行 时序功能仿真,结果如图7所示。

由仿真结果,不难看出,来自于光电编码器的初始 信号CA,CB 经过四倍频逻辑电路处理,输出CAA 和 CBB 信号,两路脉冲信号频率满足四倍关系。当脉冲 CAA 在上升沿时,判断CBB 脉冲电平值,如果CBB 为 高电平,表示电机反转,将判向信号DIR 置为0;反之, 则为电机正转,将判向信号DIR 置为1.判向逻辑电路工作符合设计要求。

3.3 脉冲计数电路仿真结果验证

对脉冲计数电路进行时序功能仿真,仿真结果波形如图8所示。

每当计数逻辑电路接收到一个有效的正转脉冲信号CAA 时,正转计数器COUNTER1 计数值增加1;每当接 收到一个有效的反转脉冲信号CBB 时,反转计数器COUNTER2 计数值增加1.当和CLK0 信号的上升沿对齐时,将COUNTER1-COUNTER2 赋值给绝对计数值COUNTER。

另外图8中的ZERO 清零信号和CLOAD 预置信号也正常工作,当ZERO 信号有效时,对计数器COUNTER1 和COUNTER2 同时清零,从而两者计数值运算后为0. 当CLOAD 信号有效时,对计数器COUNTER1 预置系统 需要的值,而对计数器COUNTER2 预置值0.通过仿真 不难发现,计数器均采用沿计数器方式,保证计数迅速和不漏码。

3.4 计数脉冲防干扰仿真结果验证

防干扰逻辑电路输入,接入经过四倍频判向电路处理后的计数脉冲信号CAA 和CBB。设置采样信号CLK0的频率为100 kHz,进行时序功能仿真后各信号的输出时序波形如图9所示。

根据仿真波形图可知,原先CAA 和CBB 两列计数 脉冲上,存在若干导致误计数发生的干扰毛刺信号,由 于所设计的DIR 信号和CLK0 信号共同实现的选通作用,将这些误计数脉冲信号完全过滤掉并且分别输出了正确 的带判向功能的两列脉冲输出信号CAAOUT 和CBBOUT。

4 结束语

本文设计的一种采用光电编码器作为测角元件、可编程逻辑器件CPLD 为核心的测量信号电路,相较于传 统的测角测量电路系统,大幅度提高了测角系统的性能, 具有一系列的优点,具体如下。

( 1 ) 工作频率高。所采用的EPM7256AETC-10 芯 片,其最高稳定工作时钟频率可以达到95.2 MHz,假设 采用50 MHz 外部时钟给定,四倍频电路要求输入脉冲频率要低于时钟频率的1/8.则输入的最大计数脉冲频率 可达6.125 MHz。

(2 ) 测角精度高。如果采用高分辨率的光电编码器 ( 例如:18 000 线光电编码器)和高倍频数的细分器 ( 例如:搭配10 倍频器),整个测角系统的最高分辨率 可以达到0.000 5°。

(3 ) 可以测量高转速。如果按照输入计数脉冲频率 6 MHz 计算,选用的光电编码器最大响应转速6000 r/min, 分辨率18 000 线搭配10 倍频器,则理论上最大可以应用 到转速480( ° )/s 的场合。

(4 ) 系统集成度高,便于通道扩展,总功耗低。可 以采用几片相同容量的芯片设计信号调理器进行并联, 从而可以很方便地扩展到多条测角通道[15] 。

另外,针对计数脉冲产生干扰信号的原因进行分 析,对测角电路系统的内部逻辑电路进行改进,并通过时序图的仿真验证了所设计抗干扰信号方法的有效性。目前,该角位置测量电路设计已广泛用于稳定平 台伺服控制系统中,应用效果良好,未来可进一步推广和使用。

参考文献:

[1]吴艳敏,黄春,崔光照.基于STC12C5410AD 的转台控制系统 的设计与实现[J].郑州轻工业学院学报(自然科学版), 2011.26 ( 1 ):59-61.

[2 ] 杨华晖,冯伟利,刘福,等.转台工作面角位置测量装置误差 分析与补偿[J].仪器仪表学报,2017.38(5):1184-1189.

[ 3 ] 周会达.基于RTLinux 的高精度角位置测量系统设计与实现 [ J ].电子测试,2016( 17 ):4-5.

[4]翁孚达,周起华.步进电机闭环伺服系统的高精度控制[J]. 制导与引信,2013.34( 1 ):13-17.

[ 5 ] 胡东轩.永磁交流伺服系统多种位置检测与集成方法研究[ D ].杭州:浙江理工大学,2014.

[6]龚寄,何雅槐.考虑转速滤波的交流永磁同步电机位置伺服 系统自抗扰控制[J].装备制造技术,2022(10):46-48.

[7]李俊颖,杨志军,邝俊澎.基于FPGA 的永磁同步电机伺服控 制系统设计[J ].机电工程技术,2021.50(9 ):30-32.

[8]殷严刚.一种混合式系留无人机高度伺服系统控制方法研究 [ J ].广西物理,2021.42(3 ):7-12.

[9 ] 张圣超,佘洪波.基于FPGA 的增量式编码器接口电路的设 计[J ].电气技术,2014( 1 ):38-41.

[ 10 ] 冯希,梁雁冰,张涛.基于FPGA 的多路增量式光电编码器 测角电路设计方法[J].现代电子技术,2008(19):175-177.

[ 11 ] 王俊山,程明,白小营.基于FPGA 的增量型光电编码器抗 抖动二倍频电路设计[J ].现代电子技术,2010.33 ( 9 ): 157-159.

[ 12 ] 王飞,付晶,韩昌佩.基于FPGA 的绝对式圆感应同步器测 角系统的设计与实现[J ].红外,2017.38 (8 ):31-36.

[ 13 ] 陈赘,李秀茹,张红胜,等.高速高冲击性小型增量式光电 编码器的研制[J]. 电子测量与仪器学报,2013.27 ( 10 ): 916-921.

[ 14 ] 王林剑.基于CPLD 的32 × 32 数字交换芯片设计及其VGA 矩阵集成应用[D].济南:山东大学,2010.

[ 15 ] 袁保伦,陆煜明,饶谷音.基于AD2S82A 的多通道测角系 统及与DSP 的接口设计[J ].仪表技术与传感器,2007 (3 ):54-55.

作者简介:

杨睿(1982—),男,实验师,硕士,研究领域为电机与电器和智能控制技术。

夏涛(1990—),男,博士,讲师,研究领域为电机设计技术和智能电网控制。

黄瑛(1969 —),女,硕士,副教授,研究领域为变速恒频风力发电。

关注SCI论文创作发表,寻求SCI论文修改润色、SCI论文代发表等服务支撑,请锁定SCI论文网!

文章出自SCI论文网转载请注明出处:https://www.lunwensci.com/ligonglunwen/65024.html