SCI论文(

www.lunwensci.com)

摘要:能量分辨中子成像谱仪是中国散裂中子源的在建谱仪,其衍射探测器90°分区采用6LiF/ZnS中子探测器作为探测设备,对成像空间分辨能力提出了更高的要求。为了提高中子闪烁体探测器的位置分辨能力,电子学系统提出了利用重心法实现数据采集电路,并研制了配套的读出电子学样机。该系统主要包括数据采集电路、前置放大电路和数字读出电路3个部分,分别实现:高效采集6LiF/ZnS中子探测器发送的数据、将探测器探测到的微弱信号进行放大整形、处理经放大滤波后的信号。在实验室分别利用万用表、示波器和信号产生器对电子学系统调试完成后,最后在中国散裂中子源20号束线带束进行了相关参数测试,束线测试结果表明,探测器位置分辨能力达2mm,满足工程设计指标。

关键词:FPGA,闪烁体探测器,重心法,SiPM

Development of Readout Electronics for High Resolution 6LiF/ZnS Neutron Scintillator Detector

Wan Zhiyong1,2,3,Huang He1,Chen Shaojia2,3※,Zhu Zhifu1,2

(1.Engineering Research Center of Nuclear Technology Application(East China University of Technology),Ministry of Education,Nanchang 330013,China;2.Institute of High Energy Physics,Chinese Academy of Sciences(CAS),Beijing 100049,China;

3.Spallation Neutron Source Science Center(SNSSC),Dongguan,Guangdong 523803,China)

Abstract:The constructing Energy Resolved Neutron Imaging(ERNI)spectrometer at the China Scattering Neutron Source uses a 6LiF/ZnS neutron detector as the detection device for its diffraction detector 90°partition,which places higher requirements on the imaging spatial resolution.To improve the position resolution of the neutron scintillator detector,an electronics system method was proposed with implementation of a data acquisition circuit using the center of gravity method and a supporting readout electronics prototype was developed.The system consists of three main parts:a data acquisition circuit,a pre-amplification circuit and a digital readout circuit.They can achieve respectively the functions as:efficient acquisition of data sent by the 6LiF/ZnS neutron detector,amplification and shaping of the weak signals detected by the detector,and processing of the amplified and filtered signals.After debugging the electronics system in the laboratory using a multimeter,an oscilloscope and a signal generator,the relevant parameters were finally tested in the China Scattered Neutron Source#20 beamline strip beam.The beamline test results showed that the position resolution of the detector reached 2mm and met the engineering design specifications.

Key words:FPGA;scintillator detector;center-of-gravity;SiPM

0引言

先进的中子源是中子科学研究的基础[1]。利用中子源可以研究材料的微观结构,促进物体微观特征的科学研究[2]。我国在20世纪50年代开始利用重水反应堆开展中子散射技术研究[3],20世纪90年代末开始在中国原子能科学研究院建造中国先进研究堆,用来开展中子散射工作[4]。作为反应堆中子源的补充,脉冲中子源具有许多优异特性,如低本低、优良的脉冲时间结构和高脉冲通量,并且不使用核燃料[5],可以实现更高能量的中子,为研究电子器件的高能中子辐照损伤提供了很好的平台。

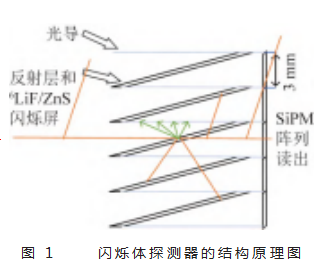

能量分辨中子成像谱仪(Energy Resolved Neutron Imag‐ing Spectrometer,ERNI)是CSNS目前在建的谱仪,是未来解决基础科学研究和关键技术的强有力的科学工具,在中子成像研究中具有广泛的应用前景。在中国散裂中子源大装置中,ERNI对成像空间分辨提出了更高的要求,为了实现谱仪要求的探测器水平方向(X方向)的位置分辨≤2 mm,读出电子学数据采集电路采用了重心法的方法来降低SiPM处理的复杂性,从而用较少的读出通道获得高分辨的位置定位结果[6-8]。ERNI的90°分区使用的是中子闪烁体探测器,探测器中SiPM把光信号转化为电脉冲信号。闪烁体探测器的结构原理图如图1所示,图中,每个扩展单元由120个SiPM紧密排布,其中每行有30个SiPM,每列有4个SiPM,单个SiPM像素为3.36 mm×3.36 mm。

1硬件电路设计

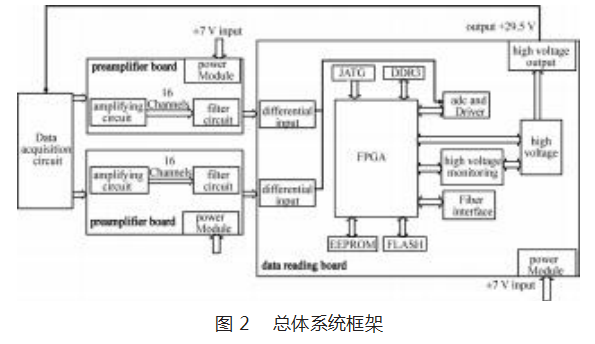

该探测器的读出电子学由3部分组成,分别为数据采集电路、前置放大电路(简称前放)和数字读出电路。为了实现探测器高位置分辨的测量要求,读出电子学数据采集电路处理SiPM输出信号,把每一行的30个SiPM通过数据采集电路连接,并在两端输出信号,有效地减少了电子学读出通道,降低了探测器后端电子学的功耗,缩小了电子学的规模;数据采集电路输出的信号经前放进行放大、滤波成一个比较平滑的信号后送给数字读出电路处理,数字读出电路首先通过高速模数转换器(An‐alog to Digital Converter,ADC)采集信号并数字化,然后由FPGA把能量信息和时间信息按照固定数据格式打包、缓存后通过以太网发送给后端上位机系统;最后根据重心法计算得到中子事例击中位置,总体系统框架如图2所示,数据采集电路实物图如图3所示。

由于数据采集电路需要处理的数据通道较多,为了提高系统的集成度,没有采用传统的数字法对每个通道的数据直接采集,而是采用重心法通过电荷再分配的方式采集SiPM输出的信号,数字法和重心法的公式分别如式(1)~(2)所示。

1.1前置放大电路

由于探测器采集到的中子信号中存在γ信号,且电子学电路板存在阻性器件,会产生热噪声,同时因为探测器输出的信号微弱,为毫伏级别,不利于后端电子学的采集分析等处理。因此前置放大电路(简称前放)把数据采集电路输出的微弱信号放大调制,再进行成形滤波清除高频噪声,使波形更加平滑,以进一步提高信噪比[9],有利于ADC模块对信号的采集和处理。

前放的实现有采用专用集成电路(Application Spe‐cific Integrated Circuit,ASIC)设计[10]和采用分立元件设计[11]两种方法。采用专用集成电路设计的前放占用空间少、体积小、功耗较低,但动态范围和增益调节不灵活。为了使得增益和动态范围调节灵敏,本文采用了分立元件设计前放。

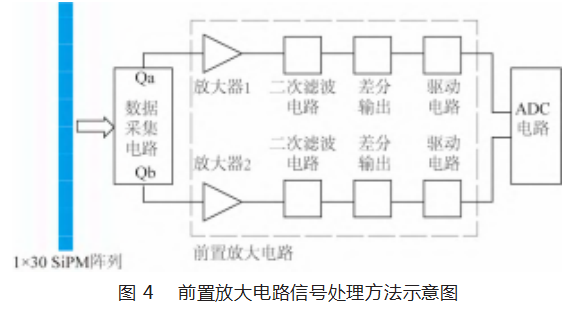

每块前放有16路电子学处理通道,其中2个电子学通道为1队,处理1组1×30的SiPM线列经数据采集电路输出的信号,每块前放可以同时处理2个4×30的SiPM阵列。读出电子学系统最多可同时使用2块前放,前置放大电路对数据采集电路的输出信号处理方法如图4所示。

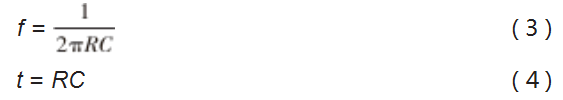

前置放大电路包括放大电路、二次滤波电路、基线调节电路和驱动电路。由于探测器输出的信号微弱,且包含杂波信号,直接采集处理不利于后续的分析,因此先要经过放电电路将微弱的电信号放大至后端ADC的全动态范围,同时还需要通过RC滤波电路滤除电路中的伽马信号和热噪声等干扰信号,将信号滤波整形成比较平滑的类指数波,从而提高测量精度。二阶RC滤波电路的截止频率和一阶截止频率一样,滤波效果更好,由式(3)~(4)和电路图可得截止频率f≈3.77 MHz,RC滤波几乎都是有源的,其电阻会导致能量损失,因此前置放大电路输出的电压在经过二阶RC滤波电路后信号幅度会衰减到0.72~0.75,后续需对此衰减进行补偿。

因为后端模数转换芯片的输入量程为±1 V,为了将经过前放处理后的信号幅度范围调节至后端高速ADC输入量程的80%,同时SiPM转换而来的电压信号是正信号,因此需要手动将基线调整为负信号。模块采用AD8137芯片,动态范围宽,是轨对轨输出低成本全差分高速放大器[12]。共模和差模分别由内部的两个反馈环控制,差模增益是由外部电阻决定,而共模电压则是由可调的Vocm控制,这样的构造可以在不改变差模增益的同时,任意设置共模电压的输出,基线调节模块电路如图5所示[12]。

此模块可以通过R233,R232等反馈电阻补偿了信号的部分衰减,同时通过改变滑动变阻器R256来改变基线大小,此设计将基线的大小调整为-800 mV,意味着将电压的最小值从0 mV拉低成-800 mV,不但保证了输出信号的电压处于后端ADC芯片±1 V的测量范围内,同时也使得前放输出的信号占据模数转换芯片的80%以上的量程。

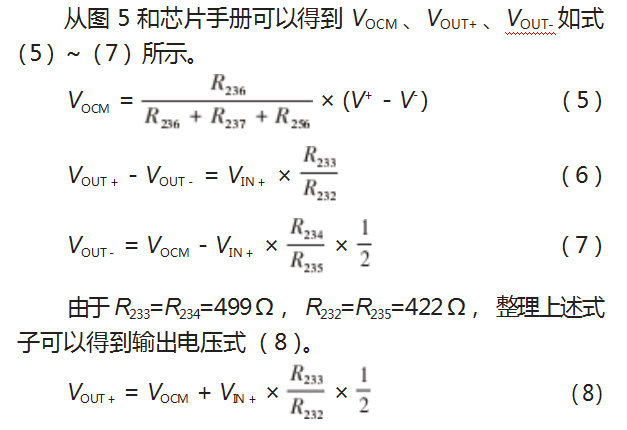

前置放大电路和后端数字读出电路通过5 m的线缆连接,信号经过滤波后再通过线缆传输。为避免远距离传输时信号衰减,需要通过驱动电路来提高信号驱动的能力。驱动电路不仅提高电路的驱动能力,还将单端的信号转换为一对差分信号,然后通过差分线缆送给后端数字读出电路的高速ADC。相比于单端信号,差分信号能有效抑制电磁干扰,抗干扰能力强[13],更适合远距离传输、较高信噪比要求的场合。前放实物图如图6所示。

1.2数字读出电路

数字读出电路主要对前放的输出信号进行采集并数字化,然后触发判选从而甄别出中子事例,在排除SiPM热噪声、伽玛等干扰信号后,把中子事例对应的幅度信息和时间信息打包、缓存,按照固定的数据格式通过光纤以太网发送给后端处理。数字读出电路同时集成了电源、高压、精密ADC、高压监测电路、温湿度监测电路、T0触发电路、JATG下载电路、驱动电路、光纤网络电路等模块,FPGA根据后端系统的命令实现模块的配置和控制,同时把相应的状态和监控信息发送给后端系统。每块数字读出电路包括32个独立的高速ADC采集通道,可以同时连接2个前放。为了更合理地实现各方面的指标要求,选择一款合适的FPGA芯片至关重要,本设计最终采用了Xilinx kintex-7系列FPGA集成电路XC7K325T-2FFG900I作为设计核心。7系列的FPGA是28 nm工艺的技术芯片,具有低功耗、高性能的优点。下面简单介绍几个主要的电路模块。

在FPGA供电中同时使用了线性电源和开关电源。开关电源具有转换效率高、抗干扰能力强、体积小、稳压范围宽等优点,其转换效率最高可达85%甚至95%[14]。

由于FPGA不仅需要给内部逻辑供电,同时为了提高FPGA的灵活性,其内部存在多种Bank,为了获得这些电平,不同的Bnak需要有不同电平标准的接口通信,因此每个Bank只能有1种I/O电压,本次设计通过外部输入±7 V电压以及电压转换芯片给kintex-7系列FPGA芯片提供±5、3.3、2.5、1.8、1.5、1.2和1.0 V几种电压,使得在一些复杂的系统中节省了大量的总线转换器。

为了实现多模块数据同步,数字读出电路使用T0信号作为触发来打包和传送缓存数据。T0是中国散裂中子源质子打靶的周期信号,周期为25 Hz,高电平大约为10µs。为了保证T0信号的可靠传输,T0信号采用抗干扰能力较强的LVPECL电平[15]。由于FPGA的I/O口不支持LVPECL电平,需要将T0信号的LVPECL转化成FPGA的I/O口支持的电平信号,因此此模块需将LVPECL转化成了LVTTL电平信号。

本设计最主要的任务是通过分析数据采集电路两端的电荷量的比值来确定中子击中的位置。由于待测的物理量是模拟信号,而FPGA内部只能处理数字信号,因此本设计采用高速ADC将前放输出的模拟信号转换为数字信号,其精度决定了整个系统的测量精度。传统的并行高速ADC需要多位数据线来传输数字化数据,不适合集成度高的应用场合。随着电子技术的发展,近年来出现了新型的高速串行接口ADC,可在不降低ADC采样率的前提下,仅通过少量的高速信号线来实现数据的海量传输,节省了PCB的面积和大量的数据口线,从而提高系统的集成度。本设计采用了TI公司的8通道、12位、电压测量范围为±1 V、最高采样率为65M的低功耗高速串行ADC芯片ADS5282。它和FPGA通过LVDS接口传输数据,每个通道仅采用一组差分LVDS线传输数据,抗干扰能力强。数字读出电路实物图如图7所示。设计完成后,为了保证数据与指令的稳定可靠传输,使用商业化的SiTCP软核实现数据与指令的交互,它采用传输控制协议/因特网互联协议(Transmission Control Protocol/Internet Protocol,TCP/IP)完成数据传输,上位机采用3次握手的用户数据报协议(User Datagram Protocol,UDP)实现对读出电子学的命令配置[16]。

2束线测试

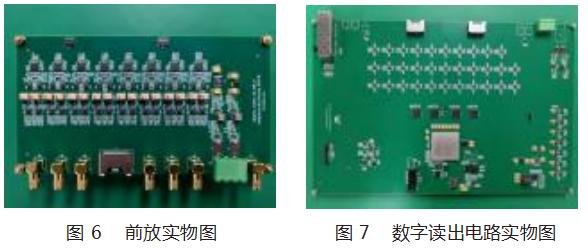

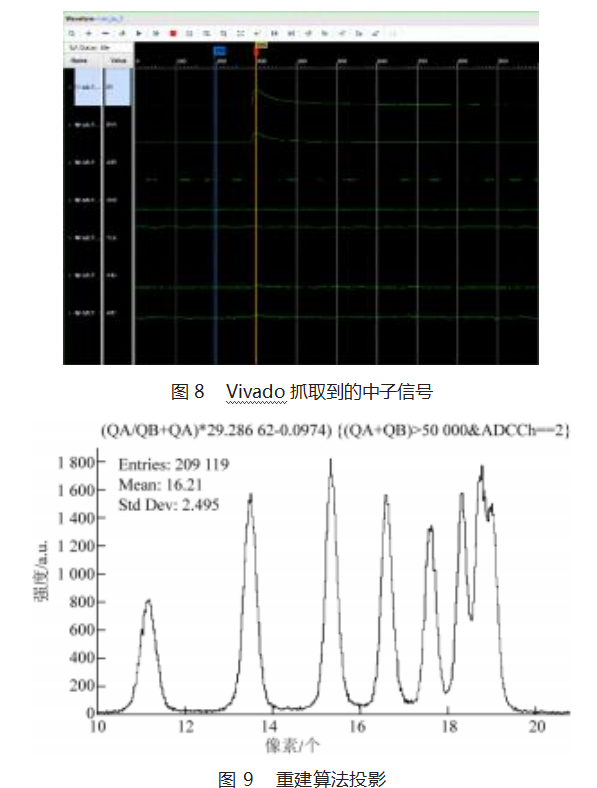

在束线测试之前需要在实验室对各个模块以及功能进行测试,修正不达标的模块。为了验证研制的读出电子学是否满足高位置分辨中子闪烁体探测器的物理设计指标,在中国散裂中子源20号中子束线开展了探测器位置分辨和探测效率实验。中国散裂中子源20号中子束线的中子能谱范围是(1~5Å),通过云母单色器把入射中子单色为单能或准单能中子(1.6Å和2.8Å)。为了测试探测器位置分辨能力,把由热中子阻挡材料加工的狭缝阵列(共8条缝,狭缝宽度均为0.5 mm,从左至右狭缝边缘间距分别为8、6、4、3、2、1、0.5 mm)放置在探测器样机入射窗前,狭缝阵列垂直于探测器水平方向,只有能够穿越狭缝的中子能够被探测到,最后由上位机的重建算法解析后得到狭缝阵列的图像,Vivado软件抓取到的中子信号如图8所示,重建算法投影图像如图9所示。从投影图中可以清晰地看到2 mm的狭缝,满足设计指标。

3结束语

为了满足能量分辨中子成像谱仪在成像空间分辨更高的要求,本文介绍了用于能量分辨中子成像谱仪的高分辨6LiF/ZnS中子闪烁体探测器读出电子学的研制,提出了一种利用重心法实现的数据采集电路,实现探测器高位置分辨的方法,同时还包括设计了前放和数字读出电路,组成一套电子学系统,该电子学系统包括数据采集电路、前放和数字读出电路。该电子学系统首先在实验室进行了模块测试,调试完成后在中国散裂中子源BL20号中子束线的测试中实现了高位置分辨。实验室和束流测试结果表明,该读出电子学达到了工程设计指标。其研制成功为能量分辨中子成像谱仪保质保量完工、顺利开展谱仪实验提供了可靠的保障。

参考文献:

[1]唐彬,孙志嘉,许虹,等.通用粉末衍射仪上位置灵敏型闪烁体中子探测器研究[C]//中国核科学技术进展报告(第四卷)——中国核学会2015年学术年会论文集第9册(核技术经济与管理现代化分卷、核电子学与核探测技术分卷、核测试与分析分卷),2016-04,中国四川绵阳.北京:中国原子能出版社,2015:224-231.

[2]杜秋宇,江晓山,李绍富,等.GEM探测器读出电子学ADC采样系统设计[J].核电子学与探测技术,2015,35(4):399-402.

[3]赵志祥.反应堆上的热中子散射研究展望[J].现代物理知识,2000,12(6):2.

[4]周健荣,孙志嘉,陈元柏,等.一种基于硼转换多级网格气体的中子探测器:ZL201810029548.7[P].2019.

[5]黑大千.PGNAA在线分析技术的发展与现状[J].科技资讯,2014,12(6):63-64.

[6]牛德芳.基于位置灵敏探测器的电子学系统的研制[D].兰州:西北师范大学,2020.

[7]陈陶,李智焕,叶沿林,等.二维位置灵敏硅探测器的应用研究[J].高能物理与核物理,2003,27(1):72-75.

[8]王英杰.基于硅光电倍增管的位置灵敏探测器技术研究[D].北京:中国科学院大学,2013.

[9]ZHOU W,ZHANG Z M,LI D W,et al.A QTC-based signal read‐out for position-sensitive multi-output detectors[J].Nuclear Sci‐ence and Techniques,2016,27(5):73-79.

[10]肖腾飞,张研,王庆娟,等.多阳极光电倍增管读出ASIC设计[C]//第十六届全国核电子学与核探测技术学术年会论文集(上册),2012-08-28,绵阳.成都:中国核学会,2012:137-141.

[11]陈少佳,赵豫斌,曾莉欣,等.CSNS工程GPPD谱仪主探测器读出电子学的研制[J].核技术,2019,42(6):39-45.

[12]傅永杰.关于FPGA在ASIC设计中的作用问题探讨[J].今日电子,1996(S1):140-141.

[13]许竞竞,李刚.高速差分ADC驱动放大器AD8137及其应用[J].国外电子元器件,2005(7):70-71.

[14]史学良.差分信号无参考平面时的阻抗装配装置及阻抗控制方法:CN104967426A[P].2015-10-07.

[15]万斌.高效率峰值电流控制升压DC-DC转换器设计[D].西安:西安电子科技大学,2010:12-13.

[16]王为民,林先钗,汤伟男.一种用于磁共振成像系统的光纤以太网通信接口:CN 204031180 U[P].2014-12-17.

[17]唐靖宇.白光中子源及其多学科应用[J].中国基础科学,2020,22(4):22-31.

关注SCI论文创作发表,寻求SCI论文修改润色、SCI论文代发表等服务支撑,请锁定SCI论文网!

文章出自SCI论文网转载请注明出处:https://www.lunwensci.com/ligonglunwen/60533.html