SCI论文(www.lunwensci.com)

摘 要:为了满足托卡马克装置放电后 CO2 色散干涉仪中数据离线分析需求,本文设计了基于 PXIe 平台的数据采集卡。 该采集卡选用了采样率为 20MS/s 的 ADC,使用了 FPGA 作为数据传输与处理的主要芯片,通过 PXIe 总线以直接内存访问 (Direct Memory Access) 的方式将实时采集数据传输到主机端。测试结果表明,该采集系统单卡测试带宽可达到 2GB/s,远 远满足 ADC 数据 80MB/s 的带宽,能够稳定地将实时采集数据完整地传输到主机中,完全符合离线分析性能需求。

Design of the CO2 Dispersion Interferometer Data Acquisition Card Based on FPGA

LI Tianyang, CHEN Xingjie, DENG Weihao

(School of Urban Rail Transit, Shanghai Polytechnic University, Shanghai 201600)

【Abstract】:In order to meet the requirements of data offline analysis in CO2 dispersion interferometer after discharge, the data acquisition card based on PXIe platform is designed. The acquisition card selects the ADC with a sampling rate of 20MS/s, uses FPGA as the main chip for data transmission and processing, and transmits the real- time acquisition data to the host terminal by DMA through the PXIe bus. The test results show that the single-card test bandwidth of the acquisition system can reach 2 GB/s, far meeting the bandwidth of 80 MB/s of ADC data, and can stably transmit the real-time acquisition data to the host completely, fully meeting the requirements of offline analysis performance.

【Key words】:PXIe;FPGA;data acquisition;CO2 dispersion interferometer

0 引言

CO2 色散干涉仪是一种托卡马克装置上实现等离子 体密度测量的核仪器,其有能够适应等离子体快速变化 且避免机械振动带来的干扰的优点 [1]。在托卡马克装置 放电后,数据中心需要对放电时装置内部的等离子体密 度进行离线分析, 因此需要采集 CO2 色散干涉仪探测 器端的输出信号。在实际放电过程中,需要对托卡马克 装置多个位置的等离子体密度进行离线分析,因此,就 需要一套能够适应多卡多通道实时高速采集的数据采集 系统。

基于以上问题,本文基于现场可编程门阵列 (FPGA) 设计了专用于等离子体密度离线分析的 PXIe 数据采集 卡。该卡采用 AD9269BCPZ-20 该款双通道,20MS/s 采 样率的 ADC,并通过 PXIe 总线将多张采集卡的原始数据上传至上位机中。测试结果表明该框架数据传输稳定 可靠, 单张采集卡数据平均传输带宽可达到 2GB/s, 完 全满足实际应用需求。

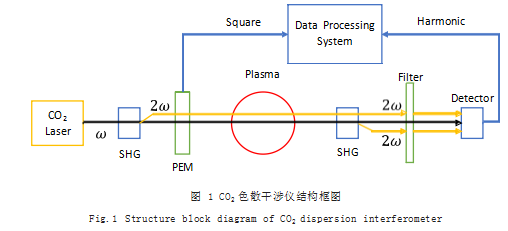

1 CO2 色散干涉仪整体结构

干涉仪整体结构如图 1 所示, CO2 激光器发出波长 为 10.6μm 初始方向为垂直的激光后,经过第一次倍频 以后产生一束偏振方向为水平的倍频波,再经过调制频 率为 50kHz 的光学弹性调制器与等离子体以后,在第 二次倍频处再次产生一束偏振方向为水平的倍频波 [2]。 滤光片将方向为垂直的基波消除后,在探测器处进行混 频,就可得到数据处理系统所需要的信号。通过求得谐 波中频信号的幅值比,再乘以等离子体密度系数,便可 得到等离子体密度。

图 1 中的数据处理系统由数据采集卡与 PXIe 机箱组成,每当放电之前,控制大厅会给触发 (Trigger) 一个高 电平,通知开始装置放电, PXIe 机箱通过实时监测板卡 触发状态,当触发到来时,机箱配置板卡开始采集 ADC 数据,并通过直接内存访问 (Direct Memory Access) 的 方式将数据传输到上位机中。采集的数据可以暂存到 DDR3 中,每次放电结束之后,可以通过 PXIe 总线将 DDR3 内部的数据上传到中控大厅中,最终实现数据的 离线处理。

2 采集系统设计与实现

现场可编程门阵列 (FPGA) 是数据采集系统的核心 模块。FPGA 内部具有丰富的 IO、RAM、DSP、Serdes 等资源,且具有强大的并行处理能力,因此被广泛应用 于军工航天等领域中。采集系统以 FPGA 作为控制器, 将数据实时采集。在 Altium Designer 中完成硬件电 路设计,在 Vivado 2017.4 中完成 FPGA 程序的设计。

2.1 硬件电路设计

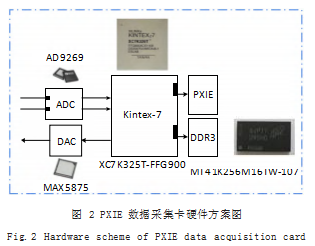

CO2 色散干涉仪数据采集卡的硬件方案如图 2 所 示,整个采集卡主要分 FPGA 主控模块、ADC 采样模 块、DAC 反馈模块、PXIe 传输模块以及 DDR3 存储模块。下面以 ADC 采样模块进行说明。

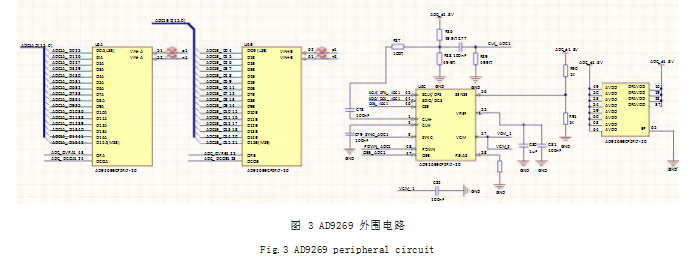

如图 3 所示为 ADC 的电路部分。AD9269BCPZ-20 是一种双通道, 16 位分辨率,采样率为 20MS/s 的模数 转换器, 其供电电压为 1.8V, 连续时间 ∑-△架构可 有效实现高动态范围与高带宽采样。其内部集成了抽取 滤波器,采样速率转换器, PLL 时钟乘法器与基准电压 源,可以通过 SPI 接口配置其工作模式。

2.2 FPGA 逻辑设计

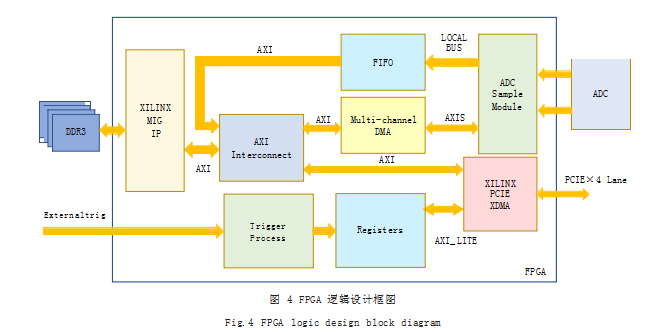

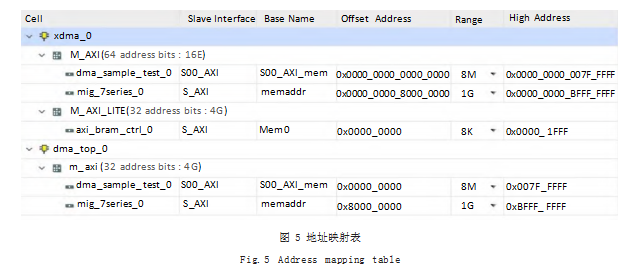

FPGA 逻辑的整体架构如图 4 所示,上位机与采集 卡通过板卡内部的寄存器 (Registers) 来进行交互。当采 集卡开始工作时, ADC 采集到的两路数据分两路存储, 一路存储到用作实时传输缓冲区的 FIFO 中,另一路存 储到 DDR3 中。存储到 DDR3 中的数据经双通道 DMA 模块, 并通过 AXI 总线互联矩阵 (AXI Interconnect) 传 输到 DDR3 控制器中, DDR3 控制器负责控制 DDR3 的读、写和刷新。每次放电开始前,硬件触发检测模块 负责检测硬件触发的到来,并将硬件触发到来状态写入 板卡内部寄存器中。上位机负责检测板卡内部寄存器的 状态,从而确定是否获取板卡内部数据。放电时,上位 机通过 DMA 方式获取暂存在作为数据实时传输缓冲区 的 FIFO 内部的数据。等到放电结束后,直接内存访问 模块 (Direct Memory Access) 通过 AXI 总线互联矩阵将 DDR3 上的数据上传到上位机中。为了方便将实时采 集数据与暂存在 DDR3 中的数据分离,本设计选用了地 址映射的方式分离两路数据,如图 5 所示为本设计中的 地址映射表, AXI 总线通过访问不同的地址空间来获取 放电时的数据与放电后的数据。

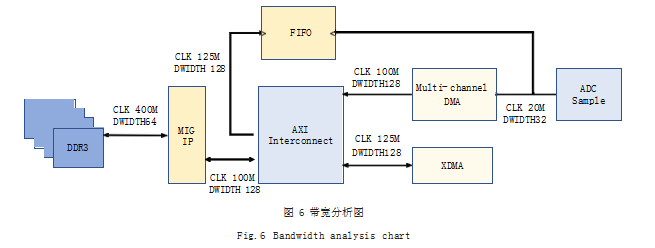

如图 6 所示为 FPGA 逻辑的带宽分析图,下面对该 图进行说明。

2.2.1 FIFO 缓冲模块

FIFO 缓冲模块具有将 ADC 采集的数据暂存,并将 数据跨时钟域以及位宽拼接的功能。FIFO 输入的时钟为 20MHz, 位宽为 32bit。FIFO 输出的时钟为 125MHz, 位宽为 128bit。将输入输出带宽分析可得输入带宽为 20×32.输出带宽为 125×128.可见输入带宽远小于输 出带宽,这样在系统运行的过程中就避免了出现 FIFO 溢出的情况,从而保证了数据的正确性。

2.2.2 PXIe 传输模块

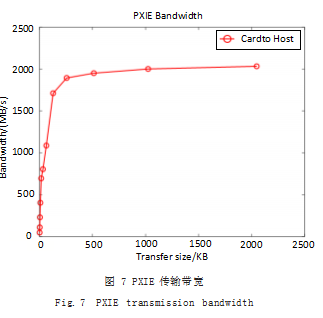

考虑到数据速度为 80MB/s,用千兆以太网传输数据 会出现数据包丢失情况。为了稳定地将完整的数据传输到 上位机中,本文采用了 PXIe 接口用于传输数据。PXIe 选 用了 GEN2. x8. 单条链路带宽能够达到 5GT/s。由于 传统的 IO 读写模式无法有效地提升 PXIE 的数据带宽, 本文选用了分散聚合式直接内存访问 (SGDMA) 的方式 来采集数据,这种方式有效地减少了处理器的负载,并 提升了带宽。在实时传输过程中, DMA 通过 AXI 总线 选择地址映射为 0x00000000 ~ 0x7FFFFFFF 的区域, 来读取 FIFO 内部的数据。在放电结束后通过选择地 址映射为 0x80000000 ~ 0xBFFFFFFF 的区域来读取 DDR3 中的数据。通过上位机的带宽测试程序,测试不 同传输数据量大小下多次传输速度的平均值,可以得到 在满带宽下板卡到主机的传输的速度如图 7 所示。

图 7 显示当一次传输的数据量大于 0.5MB 时,传输带宽已接近 2GB/s,因此本设备选择一次传输 0.5MB 的 数据,远远满足实时传输数据的带宽需求。

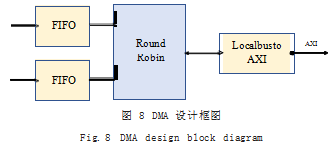

2.2.3 DDR3 读写模块

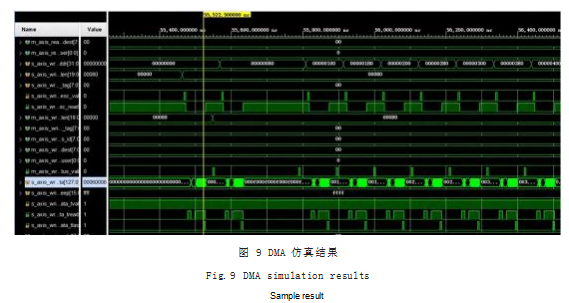

本采集卡选用四片型号为 MT41K256M16TW-107 的 512MB 的 DDR3 组成 2GB 的存储空间。为了减少板级 功耗, 提供给 DDR3 的时钟变为 400MHz, 位宽为 64bit, DDR3 控制器接口时钟为 100MHz, 位宽为 128bit。为了 方便与 AXI 总线交互,以及设计模块通用化,本文专门设 计了一种双通道基于 AXI 总线的 DMA, 以便将两路数据 存入 DDR3 中。DMA 设计框图如图 8 所示,两路数据 先暂存到 FIFO 中, 轮询 (Round Robin) 模块负责依次 检测两个 FIFO 内部的数据量是否到了突发写的长度,如 果达到了突发写长度,轮询模块通过本地总线 (Localbus) 转换为 AXI 总线传输到 DDR3 中。DMA 仿真结果如图 9 所示,每次写入突发长度为 8.位宽为 128bit 的数据。在 实际测试中 DDR3 控制器连续以突发长度为 8 的情况下 工作,DDR3 写带宽可达到 200MB/s, 能够满足输入数 据为 80MB/s 的带宽需求。

3 实验结果

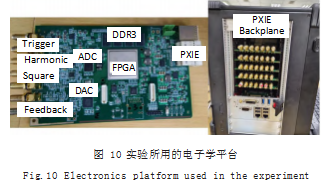

如图 10 所示为本次实验所用的电子学平台,通过 采集 SMA 接口输入的两路探测器信号, 并对数据进行 离线分析求得装置放电过程中谐波内部相位变化情况。

本实验在激光房内搭建模拟系统来验证采集数据的 准确性。在色散干涉仪系统稳定,探测器能收到稳定的谐波信号后, 通过移动 ZnSe 锲片,来模拟等离子体密 度的变化,并且按照实际放电过程中的光路距离实现模 拟测试。

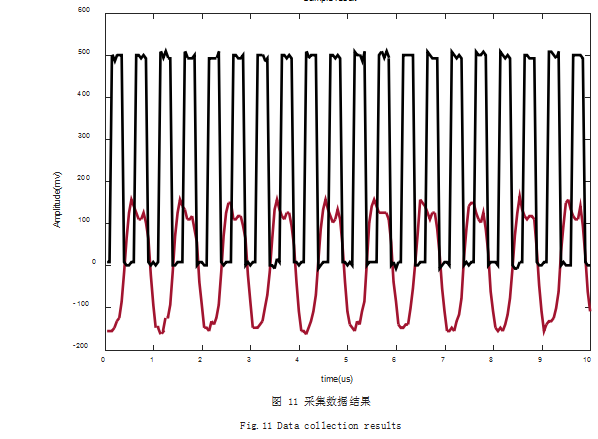

采集信号结果如图 11 所示,可以看到采集卡以 20MS/s 的采样率采集到了频率为 100kHz 的方波与频率为 50kHz 的谐波,本采集卡ADC 满量程为 -1V ~ +1V,编码量化 以后的位宽为 16bit, 数据范围为 -32767 ~ +32767.根据 ADC 的编码规则, 可以换算得方波输入幅值经过转换后 的幅值接近 500mV,而谐波的峰值在 130mV 左右浮动。

将这两路信号经过 Matlab 算法处理后,可以得到 如图 12 所示的相位变化结果。从图 12 中可以看出在约 2.5 ~ 5s 这一段时间内, 相位差因 ZnSe 锲片的移动而一直递增。这就表明了使用该数据采集卡能够正确解算 出相位结果。

4 结论

本课题基于现场可编程门阵列 (FPGA) 设计了专用 于等离子体密度离线分析的 PXIe 数据采集卡。该卡选 用 AD9269 双通道、20MS/s 采样率 的 ADC, 并通过 PXIe 总线将原始数据上传至上位机中。经过实际最大 带宽测试分析,该卡的平均传输速度能够达到 2GB/s, 满足对传输速率要求高的核仪器的实际应用。实验结果 表明,该卡能够稳定有效传输放电时的原始数据,且根 据离线计算能够得到正确的相位变化结果。

参考文献

[1] 王浩西.HL-2A装置上CO2激光色散干涉仪系统的研制[D]. 北京:清华大学,2020.

[2] 李维明.EAST上CO2色散干涉仪的研制及偏振干涉仪实验 研究[D].合肥:中国科学技术大学,2019.

关注SCI论文创作发表,寻求SCI论文修改润色、SCI论文代发表等服务支撑,请锁定SCI论文网!

文章出自SCI论文网转载请注明出处:https://www.lunwensci.com/jisuanjilunwen/62783.html