SCI论文(www.lunwensci.com):

摘要:采用Xilinx Artix-7FPGA和Cypress CYUSB3014为核心处理模块,配以DDR3作为帧存,设计了一套高速CameraLink图像采集传输系统。系统利用Xilinx Artix-7自带的ISERDESE资源将串行LVDS的CameraLink视频流转换为TTL并行信号,DDR3存储器作为帧存对输入视频进行缓存,缓存之后的视频信号经过CYUSB3014芯片转换成符合UVC协议的输出数据,通过USB3.0的数据接口发送至PC机,在PC端上能够正常显示。

关键词:FPGA;CameraLink;USB3.0;图像采集;UVC

High Speed CameraLink Image Acquisition Based on FPGA and USB3.0

LIU Yuyu,FAN Yongjie

(School of Science,Kunming University of Science and Technology,Kunming Yunnan 650500)

【Abstract】:Using Xilinx Artix-7FPGA and Cypress CYUSB3014 as the core processing device and DDR3 memory as the frame storage,a high-speed CameraLink image acquisition system was designed.Xilinx ArtiX-7 ISERDESE resources are used to convert the CameraLink video stream of serial LVDS into TTL parallel signal,and DDR3 memory is used as frame storage to cache the input video.By CYUSB3014 chip,the cached video signal is converted into output data conforming to UVC protocol and sent to PC through USB3.0 data interface,which can be displayed normally on PC.

【Key words】:FPGA;CameraLink;USB3.0;image acquisition;UVC

0引言

CameraLink作为一种重要的视频传输标准,广泛应用于工业摄像头的数据传输,以其固有的低电压、低功耗和高速传输等特点,正逐渐成为宽带高速系统设计的首选接口标准。

CameraLink在解决图像数据输出和采集之间的速度匹配问题上有很好的优势,能方便有效地实现高速数字相机和图像采集卡之间的连接和数据传输。目前,国内也有不少对于CameraLink图像采集系统的研究。哈尔滨工业大学兰功盾、赵占锋等进行了基于PCIe2.0的CameraLink接口相机模拟系统设计的研究[1],中北大学的单彦虎、张晋顼等进行了基于FPGA的CameraLink图像数据接口设计的研究[2],空军航空大学的沈鸽、长春理工大学的王美娇等人进行了对基于CameraLink的视频图像采集与传输系统的研究[3]。

以往的研究大多基于PCIe接口进行图像采集系统开发,USB接口的开发相对较少。相较于USB接口来说,PCIe接口在与计算机连接时,所能连接的数量有限,这让USB接口成为了更好的选择。其次,在以往的CameraLink图像采集系统中,除了采用FPGA作为主控芯片外,还需采用专用信号串并转换芯片(DS90CR285)才可实现数据的相互传输,专用的转换芯片将占用部分PCB面积,不利于采集装置的小型化。

基于以往研究的不足之处,本文提出了以XilinxArtix-7 FPGA和Cypress CYUSB3014为核心的高速CameraLink图像采集系统。该系统可以将串并信号转换功能在FPGA内部实现,取消专用信号串并转换芯片;同时,USB3.0数据接口使得图像采集系统更具灵活性。

1接口协议

1.1 CameraLink接口协议

CameraLink是由NI(National Instruments)、数字相机供应商和其他图像采集卡公司于2000年10月联合推出的一种基于视频应用的通信接口。CameraLink接口的数据传输采用的是低压差分信号(LVDS)形式,其数据传输速率可达2.38Gbit/s。CameraLink是在ChannelLink技术基础上发展而来的,ChannelLink使用一个并转串驱动器(Driver)和一个串转并接收器(Receiver)传输数据。驱动器将28位CMOS/TTL信号以7:1方式串行化为4组LVDS数据流,一个锁相环传输时钟通过第5组LVDS链路与其他LVDS数据流并行传输。接收器接收4组LVDS数据信号和1组LVDS时钟信号,将数据流转换回28位的CMOS/TTL并行数据信号和1路时钟信号[4]。也就意味着,使用5对线缆便可完成28位数据信号和1路时钟信号的传输,在实现高速数据传输的同时,也减少了线缆的使用数量。

在此基础上,CameraLink增加了相机控制信号和串行通信信号,定义出标准的接头也就是标准化信号线,让相机及图像采集卡的信号传输更加简单化。同时提供初级(Base型)、中级(Medium型)、高级(Full型)三种构架[5]。

1.2 USB视频协议

USB总线从推出以来就得到了广泛的应用,也是目前来说最为成功的外设接口规范,最大的特点是实现热插拔和即插即用功能。当设备插入时,主机枚举到此设备并加载所需的驱动程序,因此其在使用上远比PCI和ISA等总线方便;就其传输速度而言,远比并行端口(例如EPP、LPT)与串行接口(例如RS-232)等传统标准总线要快。USB 1.1(USB 2.0 FullSpeed)的最大传输速率为12Mbps,USB 2.0(USB 2.0 HiSpeed)为480Mbps,USB 3.0(USB 3.2 Gen1x1)为5Gbps。

2005年以微软和另外几家设备厂商为首的USB组织联合推出了UVC(USB Video Class)协议,为USB视频设备定义了协议标准,其优点在于与PC连接时不需要安装驱动,目前已成为USB org标准之一[6]。当前主流的操作系统大多内置UVC设备驱动,因此符合UVC规格的硬件设备不需要安装任何驱动程序即可在终端(如PC)正常使用。

2系统整体设计

2.1平台的构建

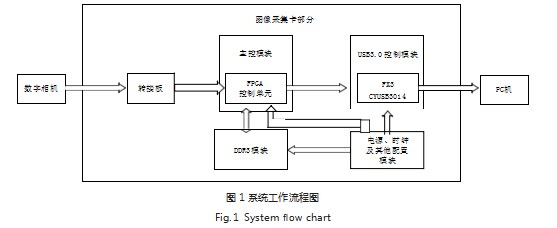

系统工作流程如图1所示:数字相机通过转接板连接到图像采集卡部分,实现高速图像数据的输入。首先,图像采集卡部分采用Xilinx Artix-7FPGA作为主控模块,因在其芯片内部集成了串并转换模块,可以直接实现在FPGA上对LVDS的CameraLink视频信号进行并行化处理。其次,采用DDR3模块作为帧存可以高效地处理输入数据。CYPRESS公司的CYUSB3014作为USB3.0控制模块的主要芯片,可以很好的实现CameraLink图像采集卡与PC机之间的连接,将采集到的数据通过USB3.0接口传输到PC端并进行显示、数据处理、存储等操作。

2.2具体实施

2.2.1图像输入

采用美国UNIQ公司的一款数字相机,其分辨率为1728×1245,帧频为16Hz,像素深度为10bit,转接板是自行设计的PCB高速电路板。根据实际要求,系统采用了Xilinx Artix-7 FPGA芯片,因其内部集成了串并转换模块,能够自行完成LVDS信号到并行TTL/CMOS信号的转换。FPGA接收数字相机经转接板传输的5对LVDS信号其中包括4对数据信号和1对时钟信号,将其转换成28位并行数据,同时分离出24位图像数据(RxOUT0~RxOUT23),4位图像数据同步信号(RxOUT24~RxOUT27),分别对应Spare、LVAL、FVAL和DVAL,只要帧、行、数据有效信号FVAL、LVAL和DVAL为高,时钟信号有效,并且数据(RxOUT0~RxOUT23)有输入即可采集到图像。

2.2.2主控模块

本次实验采用的Xilinx Artix-7 FPGA,首先,主要完成CameraLink接口通信、图像数据输入输出缓存、外设接口控制逻辑、相机控制等。其次,在其内部集成了串并转换资源(ISERDESE),在图像传输的过程中可直接实现数据的串并转换,而无需外接专用信号串并转换芯片。ISERDESE2(Input Serial-to-Parallel Converters)是一个专用的串并联转换器,具有特定的时钟和逻辑特性,旨在促进高速源同步应用的实现。

2.2.3 USB3.0控制模块

该模块是实现USB3.0高速传输的关键。选用Cypress公司的FX3系列CYUSB3014为USB3.0接口芯片,USB3.0接口与PC端互传速度为370MB/s。USB3.0控制器FX3与FPGA之间通过SlaveFIFO接口互联,可以实现大吞吐量的数据传输。图像数据最终以标准UVC协议格式发送到PC端。具体输出数据格式如下:使用8位同步并行数据接口、图像分辨率为1280×720、帧频为30FPS、每个像素深度为8位、YUV422格式等。

3测试

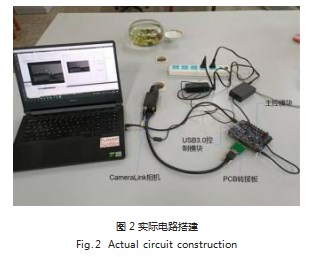

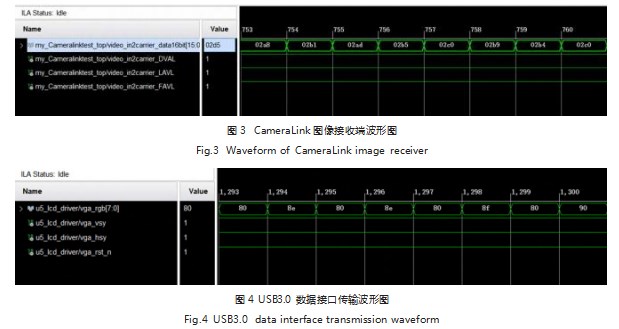

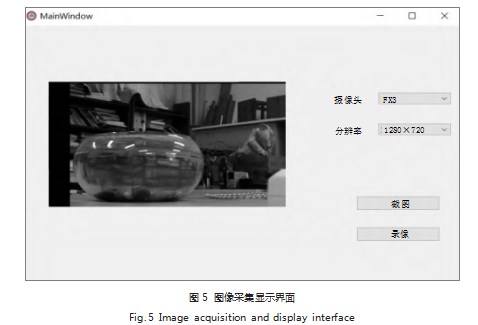

实际的电路搭建如图2所示,利用Vavido自带逻辑分析仪对实际电路进行测试,结果所下所示,图3为CameraLink端口图像输入波形的截图,当帧同步信号(FVAL)、行同步信号(LVAL)、数据有效信号(DVAL)同时处于高电位的情况下,即表示能接收到有效数据;相机发送的有效数据位宽为10bit,加之FPGA内部单个ISERDESE2的位宽只有8bit,为了实现图像数据的正常传输,故在本次实验中采用低2位截断的方式实现8bit的串并转换。如图4所示为USB3.0数据接口传输波形图,同样也是当行同步信号(hsy)和场同步信号(vsy)置于高位时开始发送数据到PC端,输出格式为YUV422,位宽为8bit。在PC端用QT Creator设计了图像显示界面,使其能够正常显示图像信息;采集结果如图5所示:采集的图像帧频固定为30帧/s,图像分辨率1280×720。

4结论

本文设计了一种基于CameraLink协议的视频图像采集与传输系统,实验中采用Xilinx Artix-7 FPGA作为核心单元,利用FPGA内部资源ISERDES实现CameraLink接口数据之间的串并转换,实现高速图像的采集和处理。运用USB3.0传输控制芯片实现将采集的视频数据转换为UVC协议标准的数据并传输至PC机实时显示。实现符合CameraLink协议的数字相机、高速图像采集卡之间的通信与控制,同时实现对图像数据的采集,实时处理、输出等功能。通过实验验证了所设计系统的稳定性和正确性,设计符合预期目标;系统稳定可靠,精度高,具有较强的通用性、实用性和扩展性,在解决高速视频图像数据传输问题上有一定的研究价值和应用前景。

参考文献

[1]兰功盾,赵占锋,魏高峰,等.基于PCIe2.0的Camera Link接口相机模拟系统设计[J].计算机测量与控制,2017,25(11):150-153+158.

[2]单彦虎,张晋顼,任勇峰,等.基于FPGA的CameraLink图像数据接口设计[J].仪表技术与传感器,2020(9):51-54.

[3]沈鸽,王美娇,嵇晓强.基于CameraLink的视频图像采集与传输系统[J].微计算机信息,2011,27(08):99-100+203.

[4]黄德天,刘雪超,吴志勇,等.基于CameraLink的高速图像采集处理系统设计[J].吉林大学学报(工学版),2013,43(S1):309-312.

[5]隋延林,何斌,张立国,等.基于FPGA的超高速CameraLink图像传输[J].吉林大学学报(工学版),2017,47(5):1634-1643.

[6]李江波,马春庭,王全,等.基于UVC协议的USB3.0视频采集系统设计[J].单片机与嵌入式系统应用,2016,16(10):31-35.

关注SCI论文创作发表,寻求SCI论文修改润色、SCI论文代发表等服务支撑,请锁定SCI论文网!

文章出自SCI论文网转载请注明出处:https://www.lunwensci.com/jisuanjilunwen/48702.html