SCI论文(www.lunwensci.com):

摘要:微处理器系统结构与嵌入式系统课程属于工科专业的一门重要学科基础课程,同时也是学生在学习电子技术类课程后的一门综合性的课程。微处理器系统结构与嵌入式系统课程涉及内容广泛,密切联系实际应用,课程需要设计实践教学环节来增强学生的理解。本文在分析课程的内容要求基础上,设计了针对该课程的综合性实践教学平台,并通过案例探讨了实践教学平台的使用。

关键词:嵌入式设计;总线访问;控制传输;实践教学

本文引用格式:赵贻玖.微处理器系统结构与嵌入式系统课程实践教学研究[J].教育现代化,2019,6(25):117-118.

一引言

随着微电子技术和计算机技术的飞速发展,越来越多的微处理器系统嵌入到各类设备中,基于微处理器的嵌入式系统应用越来越广泛[1,2]。传统的计算机接口技术课程不能满足行业的需求,在该背景下,大量高校工科专业开设了微处理器系统结构与嵌入式系统课程,并定位为高校工科专业课程体系结构中非常重要的学科基础课程。微处理器系统结构与嵌入式系统课程安排在电子技术类课程之后,课程内容涉及了数字电路、模拟电路、汇编语言编程等课程,内容涉及广泛,应用型强,是一门以应用型为主的课程,包括了课堂面授和实践教学两部分教学内容。

微处理器系统结构与嵌入式系统课程实践教学虽然是课堂面授教学的辅助,但实践教学对课程内容的理解具有非常重要的作用。学生通过课程设计的实验学习,不仅能够加深对课堂所学抽象内容的理解,还能够提升学生学习的积极性,培养学生的动手能力。因此,微处理器系统结构与嵌入式系统课程的实践教学在该课程的学习中具有非常重要的作用。

传统微处理器系统结构与嵌入式系统课程的实验设计存在诸多问题,以笔者所在教学课题组为例,所使用的实验平台通用化,类似于ARM处理器的开发板。在实际应用中,ARM处理器需要与外围部件联合工作,比如,ARM处理器与FPGA连接,通过FPGA丰富的逻辑资源和管脚资源,可以极大地拓展ARM处理器的功能,并且此种结构也是在实际工程应用中使用非常广泛的系统结构。然而,传统的开发平台设计没有考虑与FPGA的联合应用。此外,在实验设计方面,传统实验教学环节主要关注程序功能的验证、基于操作系统的驱动设计与应用,这些实验对处理器结构和嵌入式硬件结构的理解帮助非常有限。因此,对传统微处理器系统结构与嵌入式系统课程实践平台和实验设计进行改进非常必要。本文将结合微处理器系统结构与嵌入式系统课程的特点与实际工程应用的需求,探讨综合实践平台的开发与实验教学的设计。

二 实践平台开发

为了达到工科专业的培养目标,学生所需掌握的电子技术理论和系统设计原理和方法非常多,其中就包括数字电路设计、模拟电路、程序语言设计、计算机基础[4]等,这些课程知识点彼此间相对独立,而微处理器系统结构与嵌入式系统课程又非常完美地将这些基础课程融合在一起。因此,在课程实验平台设计的时候需要考虑课程在课程体系结构中的特殊性。

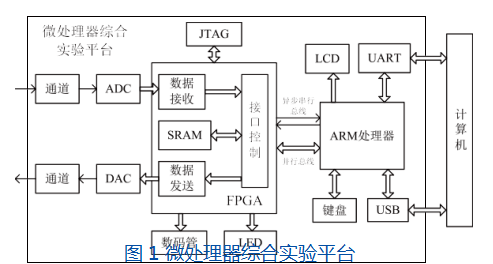

程序功能验证的相关实验由最小ARM系统就可以完成,本文所设计的实验平台主要关注ARM与FPGA、外围部件的接口信息传输方面进行讨论。所设计的综合实验平台能够融合该类专业的核心理论知识,并进行较复杂的工程验证、设计与创新训练。为此,笔者结合工程项目中的设计经验来设计一套微处理器系统结构与嵌入式系统课程综合实践平台,具体设计方案如图1所示。

该实验平台以嵌入式处理器ARM与数字逻辑器件FPGA为核心,融合了键盘输入,LCD、LED及数码管显示,信号输入采集,信号产生控制,存储器扩展等功能单元。ARM采用S3C2416处理器,FPGA采用Altera公司的EP4CE10F17C8。该实验平台中,主要功能单元电路包括:USB提供计算机调试和下载程序的通信接口,UART可以完成异步串行通信实验内容,LCD为基于嵌入式操作系统的相关实验提供显示,数码管及LED可以为基于裸机开发实验提供显示,键盘为矩阵键盘,用于无条件控制传输的实验设计。ARM处理器通过外部总线与FPGA相连,FPGA内部设计有SRAM存储器,用于设计存储器访问的相关实验,ADC和DAC单元用于设计接口输入和输出相关的实验。JTAG调试接口不仅可以用于FPGA程序下载,还可以用于对FPGA的调试,通过SignalTap软件,实现对总线时序的监测。

相对传统实验平台,本文设计的微处理器综合实验平台不仅可以开设程序功能验证类实验和基于嵌入式操作系统的相关实验,还能开设与课程教材内容密切相关的实验[3],包括:总线访问时序实验、ADC采集实验、DAC信号产生实验、存储器访问实验等。其中,ADC采集及DAC信号产生能够实现对外部接口信息传输方式中的程序查询传输和程序中断传输内容的实验设计。这些新增实验内容在传统实验平台上都无法开展,而总线时序、接口信息传输方式及存储器访问都是该课程非常重要的内容。

三 实验教学设计

在本文中[5],主要通过总线访问时序实验和基于ADC信号采集的程序查询输入实验来介绍通过本平台的实验设计。

1.总线访问时序实验:设计该实验的目的是帮助学生理解总线的时序,在ARM处理器内部时序控制电路的控制下,当ARM处理器通过总线进行读写操作时,数据总线、地址总线、控制总线会在特定时刻发生变化,总线访问时序实验的目的就是配合程序,监测总线上的时序变化。总线访问时序实验主要包括两个方面的内容:FPGA端的SignalTap软件配置和ARM的程序设计。ARM端的程序设计比较简单,可以编写一个简单程序,该程序包括外部读写功能,但程序的读写地址空间所在Bank(块)的 选择信号应输入FPGA中。在本实验中[6],监测总线时序主要是通过QUARTUS软件中的SignalTap嵌入式逻辑分析实现,在观测前,需要进行必要的配置,包括添加观测信号,如数据总线、地址总线、读/写控制线及片选线(片选线为地址空间对应的块使能信号线)。配置采样时钟及存储深度,采样时钟设置为总线操作频率的5-10倍,这样既能完整观测信号,又能避免占用过多的存储空间,为了能够准确观测信号的变化时刻,还需要将片选信号的变化设置为触发条件,启动SignalTap开始采集,运行程序,当有读写操作时即可捕获总线的变化。

2.基于ADC信号采集的程序查询输入实验:为了模拟和观察程序查询传输中的状态信号的变化,程序需要进行单步调试,由于ADC的转换速率相对单步调试的速率可以忽略不计,无法模拟出状态由无效到有效的变化过程。因此,需要在FPGA中对ADC进行控制,程序启动ADC采集后,FPGA控制ADC采集输入信号并存储采样数据,同时给出忙信号,此时程序查询到的是无效状态,经过特定时间后,FPGA给出空闲信号,此时程序查询到的状态有效,即表明采集完成,ARM程序可进行采集数据的读取。

四 结束语

针对微处理器系统结构与嵌入式系统课程的内容安排和课程在工科专业课程体系中的特殊地位,笔者结合多年的教学和工程设计经验,设计开发了微处理器综合实验平台。该实验平台以ARM和FPGA为核心,具有丰富的功能和良好的扩展性,不仅能完成传统基于ARM开发板的基础实验,还能开展电子信息综合实验和创新性实验,通过该平台设计的教学实验,对学生的动手能力和解决复杂工程问题的能力具有显著的提高。

参考文献

[1]卫建华,邓云兵,高燚,等.基于ARM的嵌入式视频采集系统的设计与实现[J].现代电子技术,2016,39(458.3):30-34.

[2]王娟.基于ARM7的嵌入式系统虚拟实验平台的设计[J].电子设计工程,2017,25(13):135-138.

[3]李广军,阎波,林水生.微处理器系统结构与嵌入式系统设计[M].电子工业出版社.2011.

[4]荆霞,李娅,赵燕飞.《计算机基础》课程教学质量提升方案研究[J].教育现代化,2016(01):99-100.

[5]徐伟.计算机网络安全课程实验教学实践研究[J].教育现代化,2018,5(18):115-116.

[6]程睦舜.开放性创新实验教学改革的研究[J].教育现代化,2018,5(34):52-53.

关注SCI论文创作发表,寻求SCI论文修改润色、SCI论文代发表等服务支撑,请锁定SCI论文网! 文章出自SCI论文网转载请注明出处:https://www.lunwensci.com/jiaoyulunwen/9088.html