SCI论文(www.lunwensci.com):

摘要:数字逻辑是计算机类、电子信息类专业培养复杂工程实践能力的一门硬件核心基础课。在传统数字逻辑课的实验教学中,存在实验依赖于硬件设备导致实验时间受限、实验验收依赖于当面验收导致无法及时反馈和验收工作量大的问题,限制了学生硬件工程实践能力培养效率。为解决上述问题,设计并实现了一种数字逻辑在线自动评测实验系统——USTB-VOJ。该系统支持Verilog的在线开发和自动评测,使得学生能够在无需教师参与的情况下随时提交实验代码并实时返回评测结果,摆脱了传统硬件课程实验对人、设备、场地和时间的依赖,大幅度提高教师和学生的效率,对学生硬件工程实践能力的培养具有较大的帮助。该系统还可以应用到计算机组成原理、集成电路设计等相关课程中。

关键词:数字逻辑;Verilog硬件电路描述语言;自动评测;在线实验

本文引用格式:张磊,等.工程教育认证背景下的数字逻辑在线自动评测实验系统[J].教育现代化,2020,7(36):1-4.

一 背景

近年来,专业工程教育认证[1]在工科专业本科教学改革、提升人才培养质量方面起到了很好的推动作用。专业工程教育受到了教育部和各大高校的广泛重视。是否通过工程教育认证也成为了入选一流本科专业建设名单的重要参考。专业工程教育认证非常重视复杂工程实践能力培养,并对实践教学课程的比例有最低要求。实验课程是承载复杂工程实践能力培养最重要的实践环节,也成为了各个各校和专业持续改进的重点,实验课程内容也越来越多从验证实验转变成设计实验[2]。对于传统实验教学来说,以下两个常见的问题严重限制了学生实践能力的培养:(1)实验依赖于实验设备和场地,导致学生实验时间受限;(2)实验结果的评价依赖于学生给老师当面演示或者教师批阅学生的实验报告,导致学生无法得到实时反馈,教师的工作量大。这两个问题严重影响了学生工程实践能力的培养。加之我国高校各专业学生人数普遍较多,使得上述两个问题造成的影响尤为突出。在线实验系统是解决设备和场地依赖和验收问题的有效方法,获得了高校的广泛认可。对于实验验收效率问题,则需要在在线实验系统的基础上,实现实验结果的自动评测。因此,在线自动评测实验系统建设对于提升工程实践能力培养、落实专业工程教育认证人才培养理念具有重要推动作用。

二 系统提出

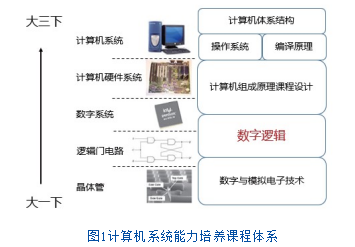

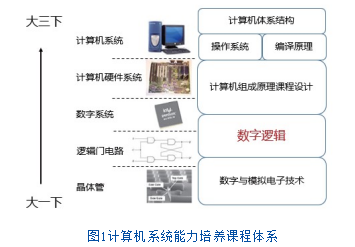

数字逻辑是计算机类、电子信息类专业培养复杂工程实践能力的一门硬件核心基础课,其主要教学目标是掌握现代的数字系统设计方法,即借助EDA工具运用硬件描述语言进行数字系统设计的方法。学生的这项能力将支撑计算机专业的CPU设计,微电子专业的FPGA和芯片设计,通信专业的基带芯片设计等。可见数字逻辑课程中培养的数字系统设计能力对后续专业课的学习至关重要。以计算机专业课程体系为例(如图1所示),数字逻辑是支持计算机系统能力培养[3]的核心基础课。

对于计算机类和电子信息类专业来说,实现硬件类课程在线实验和自动评测难度较大。目前,只有少量学校和专业开展了在线实验建设,采用的方案是将实际的硬件编程接口连接到网络实现在线下载,通过摄像头拍摄运行代码产生的现象来反馈结果[4,5]。这种方案虽然可以实现在线实验,但是没有实现自动评测,无法大幅度提升教学和学习效率。近年来,在线自动评测OJ(Online-Judge)系统在软件类课程实验中已经被广泛采用。基于OJ系统的实验教学过程中,学生在线提交程序源代码,系统对源代码进行编译和执行,并通过预先设计的测试数据来自动检验程序源码的正确性[6],并实时返回评测结果。OJ系统不仅大幅提升了教师的工作效率,也激发了学生的学习积极性,提高了编程能力[7]。由于缺少对硬件描述语言(目前主流的硬件描述语言包括verilog和VHDL)自动评测方法的研究,目前已有的OJ系统只支持软件类编程语言评测[8]。仅有硬件描述语言OJ系统的公开研究成果是文献[8]中提出的Verilog自动评测系统。该系统在自动评测方法上沿用了软件编程语言的评测方法,也就是对比运行结果的数值来判断是否正确,没有考虑信号时序问题。但对于数字逻辑系统设计来说,信号的时序和数值(也就是信号的波形)共同决定了设计的正确性。因此,对于数字逻辑实验,仅仅通过数值比较是不够全面的。所以在数字逻辑课实验教学中,仍然存在实验依赖于硬件设备导致实验时间受限、实验验收依赖于当面验收导致无法及时反馈和验收工作量大的问题,限制了学生硬件工程实践能力的培养效率。此外,该课程实验教学还存在以下问题:(1)需要大量练习才能建立硬件设计思维:逻辑课程通常安排在大二,学生在大一接受了顺序执行(串行)的软件设计思维训练,在学习初期很难将硬件描述语言构成的代码与并行执行的硬件逻辑对应起来。(2)EDA工具上手难:EDA工具由于过于专业,提供了各种各样的初学时用不到的功能,有一套比较完善但复杂的操作流程,在实际实验过程中,学生需要花费大量时间和精力来熟悉EDA工具的使用。(3)EDA工具庞大,运行时间长:数字逻辑教学中的硬件电路设计语言多采用Verilog硬件电路描述语言,学生在EDA软件中通过编辑Verilog代码描述电路功能,执行电路仿真任务。EDA工具的安装占用10G多的磁盘空间,执行仿真任务时,常常需要大量的时间,降低了学生们的实验速度。因此,数字逻辑硬件设计初学者同时面临思维转变、复杂工具安装和使用等挑战,这也一定程度上影响了学生兴趣的建立和学习效率。

为了解决数字逻辑实验的自动评测以及其他影响硬件工程实践能力培养的问题,本文设计并实现了支持Verilog自动评测的数字逻辑在线实验系统(Verilog Online-Judge from USTB,简称USTB-VOJ)。该实验系统主要具有以下特点。

(1)基于波形比较的Verilog代码自动评测,保证评测结果的全面性和正确性。

(2)在线波形显示,实现波形数据在Web浏览器的图形化显示,让学生不仅能够获得评测结果,还能够看到完整波形比较,快速定位错误。

(3)在线伴随式编程,提供在线编程环境和源程序文件提交,实时返回编译综合后的信息以及信号波形,让学生在学习初期无需庞大复杂的EDA工具就能够进行硬件描述语言练习和实验。

(4)使用轻量级的在线仿真工具,支持硬件电路综合和功能仿真,无需高性能服务器。

三 系统设计与实现

(一)系统架构

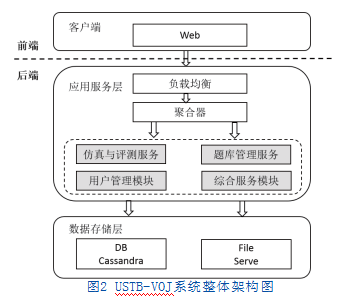

USTB-VOJ系统采用微服务架构[9],在典型的MVC三层架构的基础上,将应用服务层中的服务拆分成仿真与评测子系统、题库管理子系统、综合服务子系统、用户管理子系统四个系统中,如图2所示。仿真与评测子系统主要负责代码的仿真与评测服务,管理题目子系统主要负责题目的增、删、改、查等服务,用户管理子系统负责用户登录、权限管理,其余的服务都统一放进综合服务子系统。数据存储层中,非文件类型的数据全部存放进Cassandra数据库中,文件数据则存放在服务器中。

(二)基于Icarus Verilog的轻量级在线仿真

Icarus Verilog(简称IVerilog)是Verilog仿真和综合工具,用于功能仿真并记录仿真结果数据。这是一个小型开源仿真工具,比起大型的EDA工具,简洁的工具能够带来更好的体验,同时能满足自动评测系统对于功能仿真的需求。

(三)基于Wavedrom的在线波形自动展示

Wavedrom是可以将简单的文本描述转化为时序图或者波形的开源组件,可以嵌入到前端网页中。在后端将IVerilog记录的仿真结果数据解析成前端Wavedrom组件需要的格式,并在浏览器中显示。

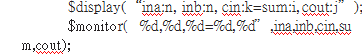

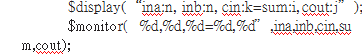

例如:假定模块的输入变量为[m-1:0]ina,[n-1:0]inb和[k-1:0]cin,输出变量为[i-1:0]sum和[j-1:0]cout,后端调用IVerilog仿真器对源代码进行综合仿真,在教师提供的测试代码模块中通过系统任务display和monitor,记录评测所需的仿真数据:

本例取m=4,n=4,k=1,i=4,j=1,如图3所示,第一行表示需要监测的变量,等号左边表示输入变量的名称和位宽,等号右边表示输出变量的名称和位宽。从第二行起,每一行表示一个时间点上,各个变量的值。

后端将仿真数据解析成Wavedrom组件需要的格式发送给前端,转换基本原理是用正则表达式匹配出变量。前端嵌入波形解析模块Wavedrom,将仿真波形数据解析成波形后在浏览器中显示如图4所示。

(四)基于波形数据比较的Verilog代码自动评测

服务器保存有与测试激励相匹配的正确波形数据,每次提交源代码后,服务器都在综合仿真结束后自动运行波形比对程序对波形数据进行评测,将评测结果数据记录并反馈给前端同时进行图形化的波形显示。

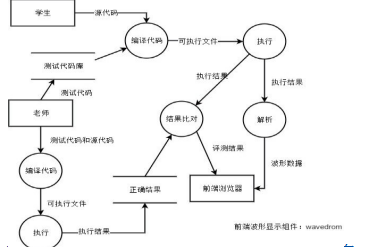

自动评测的具体过程如图5所示,USTB-VOJ系统将教师发布题目时上传的测试代码和源代码一同编译成可执行文件,执行该文件,保存正确的仿真波形数据文件。当学生在伴随式编程环境中写好电路代码点击提交后,系统将学生提交的源代码和老师出题时提交的测试代码一起编译成可执行文件,执行该文件,生成学生仿真波形数据文件。通过将正确的仿真波形数据文件和学生的仿真波形数据文件进行对比。将两个波形数据文件进行逐行对比,对比的结果有两种,一种是完全一样,一种是不完全一样。将学生的仿真波形数据文件解析成前端组件Waveform需要的格式,最后将解析后的数据和评测结果一起发送到前端浏览器。能够直接告诉用户仿真结果是否正确,如果有错误,会提示错误信息。

(五)基于Monaco Editor和GoldenLayout的在线伴随式编程

在线伴随式编程是在网页上直接编辑代码,无须用户安装EDA工具。可提供关键字和注释的特殊高亮显示,提升编码效率和体验。题目和代码编辑框同时出现一个页面中,无需来回切换页面。

如图6所示,布局是基于GoldenLayout组件,可以通过随意拖拽来改变各个模块的大小和位置。代码编辑框基于Monaco Editor组件,可以对代码中的关键字、注释、数字等进行特殊显示。

四 系统意义和价值

(一)自动评测更高效

基于波形比较的Verilog自动评测系统的评测结果更加精准直观。不仅对结果进行评判,而且对中间信号也能够进行评判。

(二)学生学习更高效

使用USTB-VOJ系统,系统能够对综合仿真结果直接给予反馈,无需学生花费时间去判断结果的正确性,学习能够得到及时有效的反馈。

(三)教师验收更高效

教师不必投入大量的时间帮助学生检查仿真结果,节省下的时间可以为学生提供更多的指导。

(四)仿真任务消耗时间更短

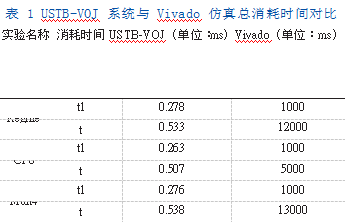

学生可以在有限的时间内,执行更多的仿真任务。以代码在50行以上的三个较复杂实验(寄存器堆Regfile,单周期处理器CPU,4位乘法器Mult4)为例,在USTB-VOJ系统与EDA工具Vivado[10]中分别将其编译综合仿真,对比仿真总消耗时间,如表1所示,仿真总消耗时间(t)=编译综合消耗时间(t1)+仿真消耗时间(t2),机器配置为2.6 GHz Intel Core i7处理器,16 GB 2133 MHz内存。可以看出在USTB-VOJ系统中的仿真消耗时间为毫秒级,而在Vivado中的仿真消耗时间为秒级。

(五)提供给学生可以针对数字系统设计进行大量练习的平台

学生数字系统设计思维的建立需要大量高质量的练习。根据教学需求开发的USTB-VOJ在线实验系统,可根据学生实际情况创建题库,学生通过大量练习掌握数字系统设计方法,能够更好地达到教学目标。

五 结语

针对数字逻辑课程教学中老师和学生遇到的问题进行在线实验系统建设,提出基于波形数据比较的Verilog自动评测系统,给出了解决方案并验证了方案的可行性。构建具有自动评测功能的在线实验系统,让系统替代教师进行验收,这样能将教师从繁重的验收工作中解放出来,将时间投入到教学内容开发和学生指导上。同时,在线评测也能让学生得到实时反馈,不须等待教师评判就能知道对错,提升实践效率。未来系统将在题库以及学生实验过程跟踪等方面进行更为细致完整的建设,更好地服务于实验教学的持续改进。USTB-VOJ系统可推广用于计算机组成原理实验等多门课程,为学生解决复杂工程问题能力的锻炼提供了较好的平台,对于整体实践教学水平的提升起到较好的促进作用。

参考文献

[1]李擎,崔家瑞,王丽君,等.面向工程教育专业认证的自动化专业课程地图设计[J].高等理科教育,2017(06):110-116.

[2] 张磊,郑榕,田军峰.计算机组成原理理论实验教学无缝结合的新方法[J].实验室研究与探索,2013,32(05):168-172.

[3 施青松,陈文智.强化计算机课程贯通教学深入面向系统能力培养[J].中国大学教学,2014(12):61-65.

[4] 李山山,陈永强,刘敬晗,等.MOOC时代下的计算机实验教学探讨[J].计算机教育,2014(13):103-106.

[5]吴先球,刘朝辉,叶穗红,等.网络环境下远程实验的技术探讨[J].实验技术与管理,2008(06):30-33.

[6]姜盼.基于协同过滤的习题推荐系统设计与实现[D].湖北:长江大学,2017.

[7]晏燕.在线编程评测系统设计与实现[D].吉林:吉林大学,2017.

[8]张德学,张小军,郭华.Verilog在线评测系统设计与实现[J].教育教学论坛,2017(29):166-168.

[9]李春霞.微服务架构研究概述[J].软件导刊,2019,18(08):1-3+7.

[10]涂丽平,于翔,史风栋,等.基于Vivado软件的数电实验教学的改革[J].教育现代化,2018,5(26):86-87.

关注SCI论文创作发表,寻求SCI论文修改润色、SCI论文代发表等服务支撑,请锁定SCI论文网! 文章出自SCI论文网转载请注明出处:https://www.lunwensci.com/jiaoyulunwen/31206.html